#### **EECE 481**

#### MOS Basics – part 2 Lecture 3

#### Reza Molavi Dept. of ECE University of British Columbia reza@ece.ubc.ca

Slides Courtesy : Dr. Res Saleh (UBC), Dr. D. Sengupta (AMD), Dr. B. Razavi (UCLA)

## **MOS Current - Review**

In general, the saturation region is entered when either the channel is pinched-off or the carriers achieved velocity saturation.

$$\text{if } V_{DS} \geq \frac{(V_{GS} - V_T) E_c L}{(V_{GS} - V_T) + E_c L} \Rightarrow \text{saturation} \\ \text{if } V_{DS} \leq \frac{(V_{GS} - V_T) E_c L}{(V_{GS} - V_T) + E_c L} \Rightarrow \text{linear}$$

$$I_{DS} = W v_{sat} C_{ox} \frac{(V_{GS} - V_T)^2}{(V_{GS} - V_T) + E_c L} \quad \text{saturation}$$

$$I_{DS} = \frac{W}{L} \cdot \frac{\mu_e C_{ox}}{\left(1 + \frac{V_{DS}}{E_c L}\right)} \left(V_{GS} - V_T - \frac{V_{DS}}{2}\right) V_{DS} \quad \text{linear}$$

Note that in extreme case ( $E_cL >> V_{GS}$ ,  $V_{DS}$ ) both equations translate to those of long channel devices

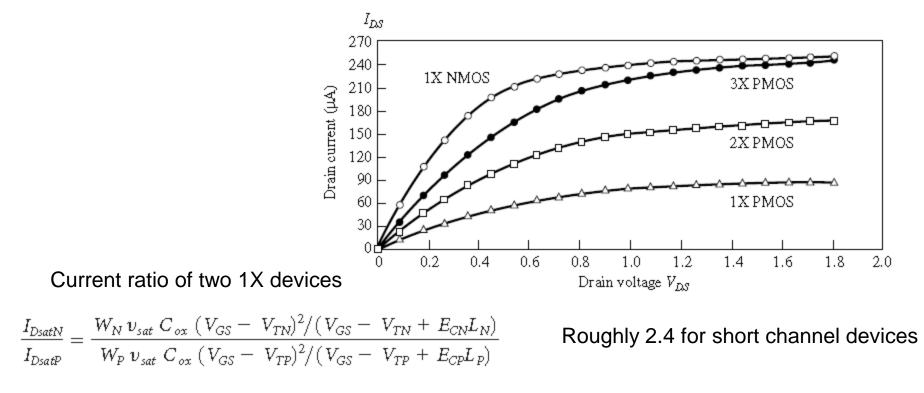

### MOS Current – Short Channel Effects

The mobility of electrons is 4X higher than that of holes, i.e. in long channel regime the current of 1X NMOS is 4times a 1X PMOS

However, early velocity saturation of electrons makes this ratio smaller in short channel devices

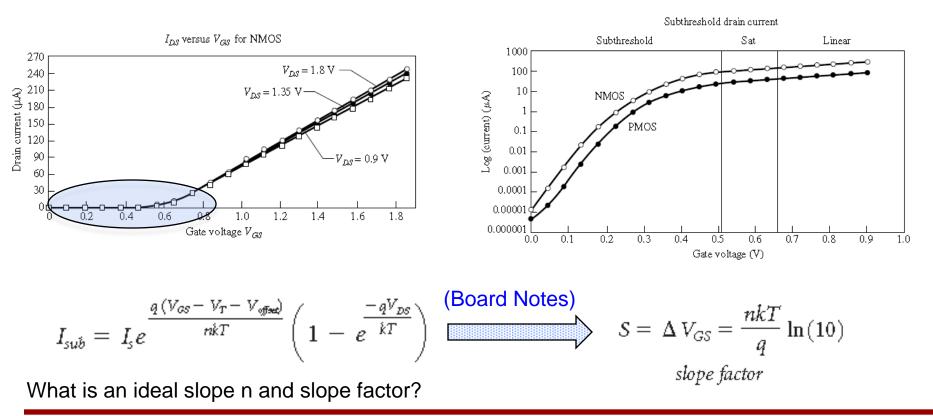

## MOS Current - Sub threshold

Transistor turn-on/turn-off switching is a continuous process. At around  $V_{th}$  (and even below it) there is still significant leakage current.

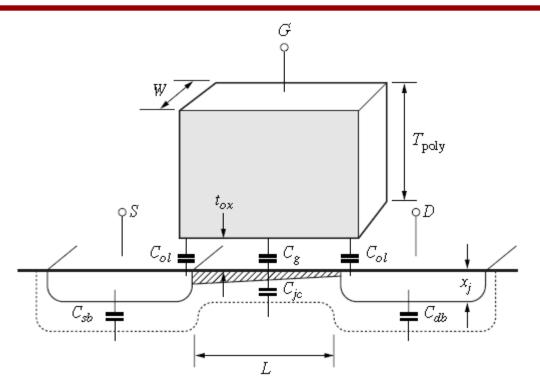

### **MOS Capacitances**

- Each MOS device possess several junction and oxide capacitances (depends on dielectric and geometry) specified in units of fF/µm

- The charge/discharge of internal capacitances limits the switching speed

### Gate (Oxide) Capacitance and DSM Evolution

$$C_G = WLC_{ox} = WL\frac{\varepsilon_{ox}}{t_{ox}} = WC_g$$

Gate Capacitance

5µm CMOS

$$C_g = C_{\alpha x}L = \frac{\varepsilon_{\alpha x}}{t_{\alpha x}}L = \frac{(4)(8.85 \times 10^{-14})}{1100}$$

(5 µm)  $\approx$  1.6 fF/µm

0.35µm CMOS

$$C_g = C_{\alpha x}L = \frac{\varepsilon_{\alpha x}}{t_{\alpha x}}L = \frac{(4)(8.85 \times 10^{-14})}{75} (0.35 \ \mu \text{m}) \approx 1.6 \text{ fF}/\mu \text{m}$$

0.18µm CMOS

$$C_g = C_{\alpha x}L = \frac{\varepsilon_{\alpha x}}{t_{\alpha x}}L = \frac{(4)(8.85 \times 10^{-14})}{22} (0.1 \ \mu \text{m}) \cong 1.6 \text{ fF}/\mu \text{m}$$

The unit capacitance has remained constant over two decades! (part of constant field scaling plan introduced in 1970)

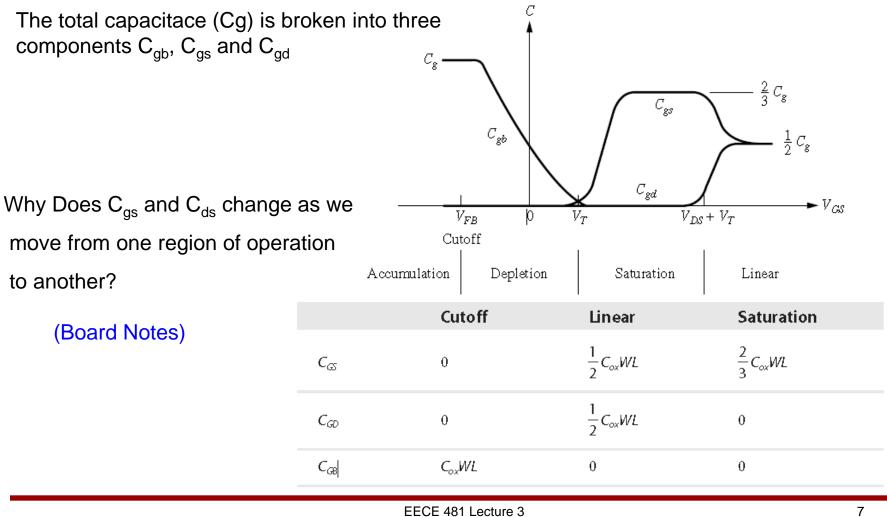

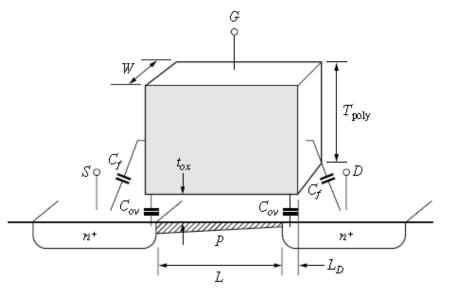

#### Gate Capacitance in different regions of operation

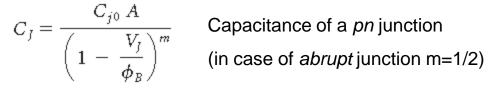

# **Junction Capacitance**

A pn junction when forward biased shows the following I-V characteristics

$$I_D = I_S(e^{V_f/V_{ib}} - 1)$$

A *pn* junction when reverse-biased has a leakage current and a wider depletion region resulting in a voltagedependant junction capacitor L

$$I_D = -I_S$$

#### (Board Notes)

Diode (junction) built-in potential

$$\phi_{\scriptscriptstyle B} = rac{kT}{q} \ln \lvert rac{N_{\scriptscriptstyle A} \; N_{\scriptscriptstyle D}}{n_i^2}$$

.

$$C_{j0} = \sqrt{\frac{\varepsilon_{si}q}{2\phi_B}} \frac{N_A N_D}{N_A + N_D}$$

Junction capacitance vs junction potentiai

## **Junction Capacitance**

#### Junction Capacitance - Example

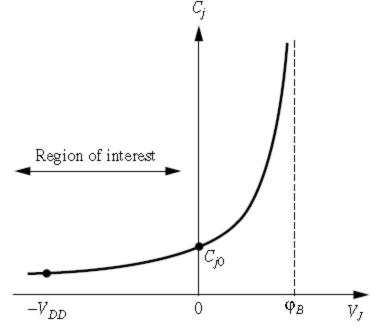

#### **Junction Capacitance Calculations**

#### Problem:

(a) Find  $\phi_{\beta}$  and  $C_{jb}$  for an  $n^+p$  junction diode with  $N_D = 10^{20}$  cm<sup>-3</sup> and  $N_A = (3)10^{17}$  cm<sup>-3</sup>.

#### Solution:

From Equation (2.37),

$$\phi_{B} = \frac{kT}{q} \ln \frac{N_{A} N_{D}}{n_{i}^{2}} = 0.026 \ln \left( \frac{3(10^{17})(10^{20})}{(1.45(10^{10}))^{2}} \right) = 1 \text{ V}$$

From Equation (2.39)

$$\begin{split} C_{jb} &= \sqrt{\frac{\varepsilon_s q}{2\phi_8} \frac{N_A N_D}{N_A + N_D}} \approx \sqrt{\frac{\varepsilon_s q N_A}{2\phi_8}} \\ &= \sqrt{\frac{11.7 * (8.85)(10^{-14}) * 1.6(10^{-19})(3)(10^{17})}{2(1.0)}} \approx 1.6 \, \frac{\text{fF}}{\mu \text{m}^2} \end{split}$$

## Junction Capacitance – Example cont'd

#### Problem:

(b) For a 0.13  $\mu$ m process, W = 400 nm, L = 100 nm,  $x_j = 50$  nm, and the diffusion extension is Y = 300 nm. Using the layout of Figure 2.20, find  $C_j$  in units of fF for and  $V_j = 0$  and  $V_j = -1.2$  V.

#### Solution:

For

$$V_j = 0$$

, the value is obtained by multiplying  $C_{jb}$  with  $(Y+x_j)W$

$C_j = C_{jb}(Y+x_j)W = 1.6 \text{ fF}/\mu\text{m}^2 \times (0.3 \mu\text{m} + 0.05 \mu\text{m}) \times 0.4 \mu\text{m} \approx 0.22 \text{ fF}$

For

$$V_j = -1.2$$

,

$C_j = \frac{C_{jb}(Y + x_j)W}{(1 - V_j/\phi_b)^m}$

$= \frac{1.6 \text{ fF}/\mu\text{m} \times (0.3 \ \mu\text{m} + 0.05 \ \mu\text{m}) \times 0.4 \ \mu\text{m}}{(1 + 1.2/1.0)^{1/2}} = 0.16 \text{ fF}$

Exercise: Use the integral (effective capacitance technique) and compare against the average here

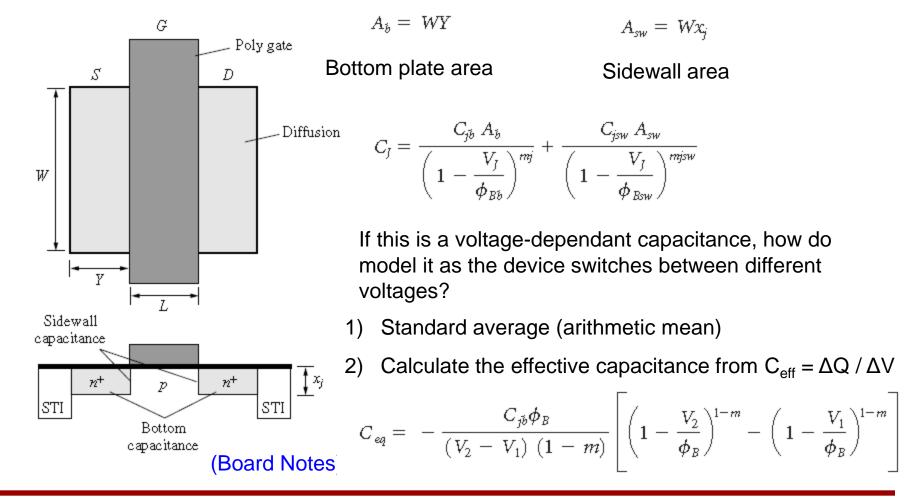

## **Overlap Capacitance**

-The lateral diffusion creates an overlap between gate and drain (source areas) creating a parasitic capacitance called *overlap* capacitance

- The proximity of drain (source) regions to the sidewall of gate in DSM contact creates another parasitic cap called *fringe* capacitance  $2e = \frac{T_{rate}}{T_{rate}}$

$$C_{ol} = C_{ov} + C_f$$

$$C_{f} = \frac{2\varepsilon_{ox}}{\pi} \ln \left(1 + \frac{T_{poly}}{t_{ox}}\right)$$

$$C_{ov} = C_{ox} \times L_{D}$$

# Summary

- The current capability ratio of NMOS and PMOS decreases (due to velocity saturation) as we move further into short channel regime.

- There is an exponential dependence of leakage current on  $V_{\rm GS}$  in sub threshold region.

- A MOS device has three main physical types of capacitance

- The gate-oxide capacitance is re-distributed between source and drain, i.e. C<sub>GS</sub> and C<sub>DS</sub> vary, as device moves from linear to saturation region.

- The junction capacitance is voltage-dependant; we need to find an effective (average) capacitance for switching devices.

- The overlap/fringe capacitance becomes more important in DSM technologies.