#### EECE 481

#### High-Speed CMOS Gate Design Lecture 9

#### Reza Molavi Dept. of ECE University of British Columbia reza@ece.ubc.ca

Slides Courtesy : Dr. Res Saleh (UBC), Dr. D. Sengupta (AMD), Dr. B. Razavi (UCLA)

#### **Effective Resistance Calculations**

## **Effective Resistance Calculations**

#### Problem:

Using 0.13  $\mu\rm m$  technology parameters, compute  $R_{eqn}$  and  $R_{eqp}$  from the equations above for unit-sized devices.

#### Solution:

For the NMOS device,

$$I_{Dsat} = \frac{W_N v_{sat} C_{ox} (V_{DD} - V_{TN})^2}{(V_{DD} - V_{TN}) + E_{CN} L_N}$$

=  $\frac{(0.1) (10^{-4}) 8 (10^6) 1.6 (10^{-6}) (1.2 - 0.4)^2}{(1.2 - 0.4) + 0.6} \approx 60 \ \mu \text{A}$

$\therefore R_{eqp} = \frac{1.2/2}{0.7 (60 \ \mu \text{A})} = 14.5 \ \text{k}\Omega$

For the PMOS device,

$$I_{Dsat} = \frac{W_{\rho}v_{sat}C_{ox}(V_{DD} - |V_{TP}|)^{2}}{(V_{DD} - |V_{TP}|) + E_{CP}L_{\rho}}$$

=  $\frac{(0.1)(10^{-4})8(10^{6})1.6(10^{-6})(1.2 - 0.4)^{2}}{(1.2 - 0.4) + 2.4} \approx 25 \ \mu \text{A}$

$\therefore R_{eqp} = \frac{1.2/2}{0.7(25 \ \mu \text{A})} = 33.5 \ \text{k}\Omega$

The HSPICE

Numbers of 12.5k-ohms

And 30k-ohm

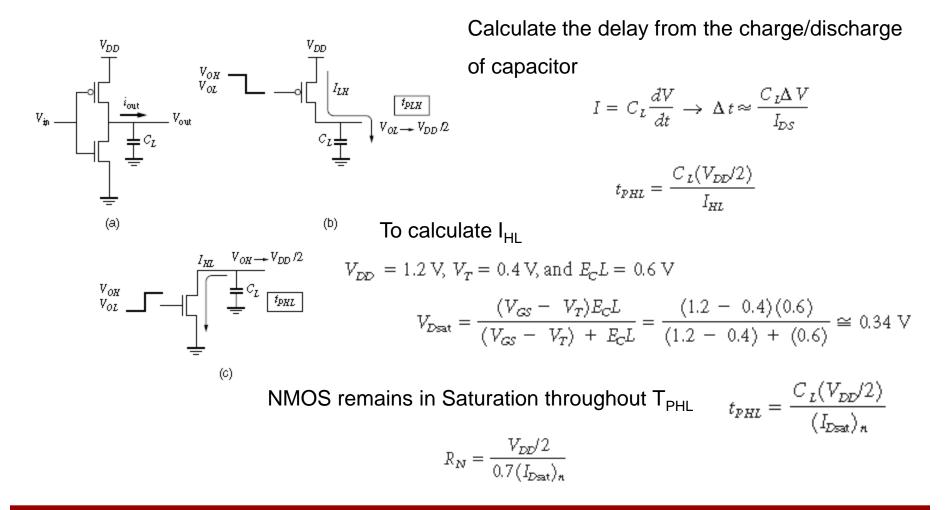

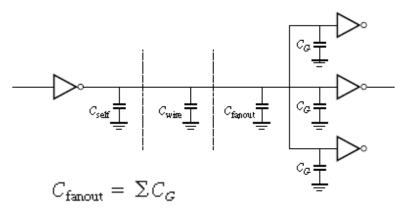

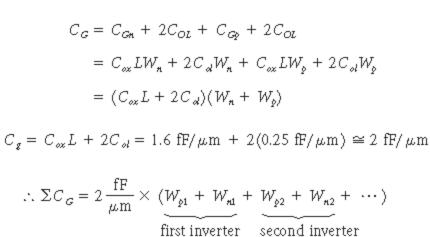

## Load Capacitance Calculations

#### "Fanout Gate Capacitance"

Each gate connected to the output of a CMOS gate (driver) presents a capacitive load, when all summed termed as "*Fanout Gate Capacitance*"

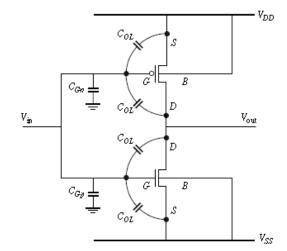

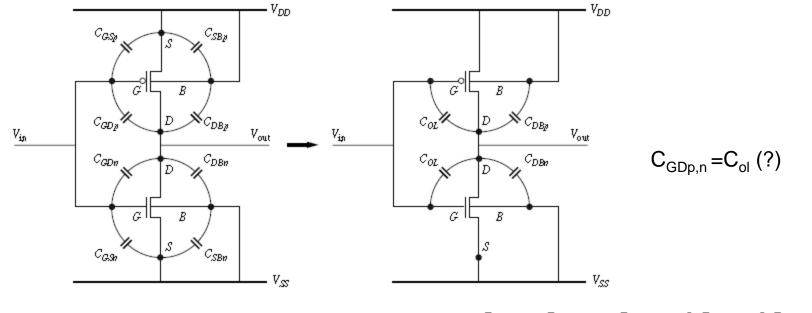

## Load Capacitance Calculations - II

"Self Capacitance"

Another term in load caclulations is the load presented by The driver itself (all capacitances connected to  $V_{out}$ ) We have to consider Miller effect! In calculating  $C_{self}$

$C_{\text{xff}} = C_{DBn} + C_{DBp} + 2C_{OL} + 2C_{OL}$  $= C_{jn}W_n + C_{jp}W_p + 2C_{ol}(W_n + W_p)$  $= C_{\text{eff}}(W_n + W_p)$

#### (Board Notes)

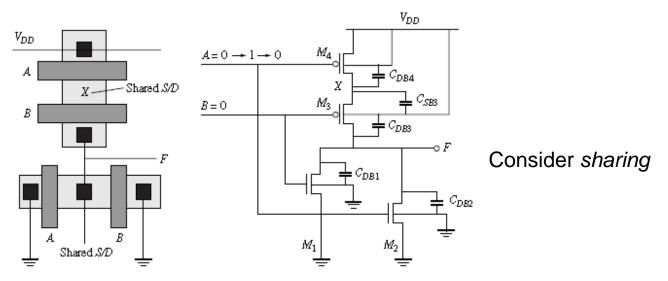

#### Load Capacitance for NAND and NOR

What is worst-case capacitance calculations, why does it matter for speed calculations?

$$C_{\text{self}} = \underbrace{C_{DB1} + C_{DB2}}_{n^{+}\text{shared SVD}} + \underbrace{C_{DB3} + C_{SB3} + C_{DB4}}_{p^{+}\text{shared SVD}}$$

$$= C_{DB12} + C_{DB3} + C_{SDB34}$$

Example: what is the worst case input and output capacitance for a NAND3 CMOS gate (Board Notes)

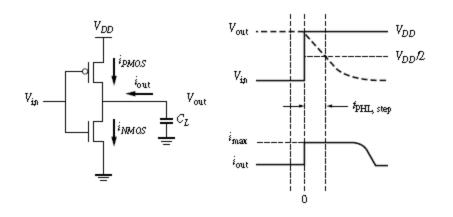

## Response of Inverter to a Ramp voltage change

Response of an inverter to a step  $V_{\text{in}}$

We modeled this propagation delay by 0.7(Ln2)\*RC (back in propagation delays)

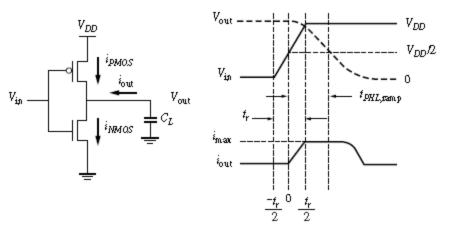

Response of an inverter to a ramp  $V_{\text{in}}$

Ramp input makes the propagation delay longer(approximately by 50%) making it  $\sim RC$

A ramp voltage change is a more realistic scenario when we have a full chain of inverters driving in cascade

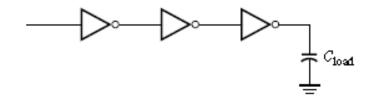

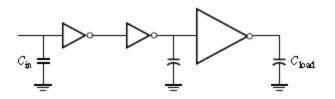

# Gate Sizing for Optimal Path delay

In order to drive a large load we can NOT use an arbitrary large gate to minimize the delay (it just shifts the problem to the previous stage)

A proper question is drive a load ( $C_{load}$ ) with an input capacitance of  $C_{in}$  (and of course optimizing the delay)

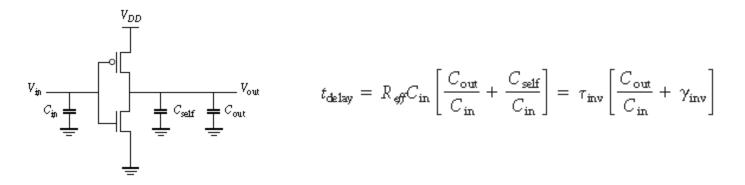

#### **Optimal Path Delay Design**

There are two unknowns, the number of gates and the size of each (two degrees of freedom)

$$C_{in} = C_{g}(W_{n} + W_{g}) = C_{g}(W_{n} + 2W_{n}) = C_{g}(3W_{n})$$

$$R_{eff} = R_{eqn}\left(\frac{L_{n}}{W_{n}}\right)$$

$$\tau_{inv} = R_{eff}C_{in} = R_{eqn}\left(\frac{L_{n}}{W_{n}}\right)C_{g}(3W_{n}) = 3R_{eqn}C_{g}L_{n}$$

This is the *intrinsic delay* of a gate (specific tag) used many places

### Gate Sizing for Optimal Path delay

total\_delay =

$$\sum_{j=1}^{N} \tau_{inv} \left( \frac{C_{j+1}}{C_j} + \gamma_{inv} \right)$$

$$c_{in} = \cdots \qquad c_{in} = c_{in}$$

$$total\_delay = \sum_{j} \tau_{inv} \left( \frac{C_g W_{j+1}}{C_g W_j} + \gamma_{inv} \right) = \sum_{j} \tau_{inv} \left( \frac{W_{j+1}}{W_j} + \gamma_{inv} \right)$$

Let's consider two consecutive ones

Minimize the delay (find a W that makes  $dD_j/dW = 0$ )

$$D_{j} = \tau_{inv} \left( \frac{W_{j}}{W_{j-1}} + \gamma_{inv} \right) + \tau_{inv} \left( \frac{W_{j+1}}{W_{j}} + \gamma_{inv} \right)$$

$$\frac{\partial D_{j}}{\partial W_{j}} = \tau_{inv} \frac{1}{W_{j-1}} - \tau_{inv} \frac{W_{j+1}}{W_{j}^{2}} = 0$$

$$\therefore \frac{W_j}{W_{j-1}} = \frac{W_{j+1}}{W_j}$$

$$\therefore W_j = \sqrt{W_{j+1}W_{j-1}}$$

If the size of each gate is the geometric mean of the two gates (previous and after) the delay Is minimum!

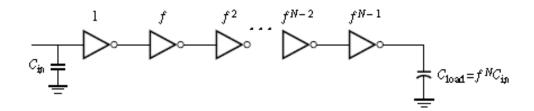

#### Gate Sizing for Optimal Path delay

Therefore, we can consider the size of gates a geometric sequence with factor *f*

$$f^{N}C_{in} = C_{ioad}$$

$$\therefore N = \frac{\ln(C_{ioad}/C_{in})}{\ln f}$$

$$total_{delay} = N \times \tau_{inv} \left(\frac{C_{j}}{C_{j-1}} + \gamma_{inv}\right)$$

$$total_{delay} = \frac{\ln(C_{ioad}/C_{in})}{\ln f} \times \tau_{inv}(f + \gamma_{inv})$$

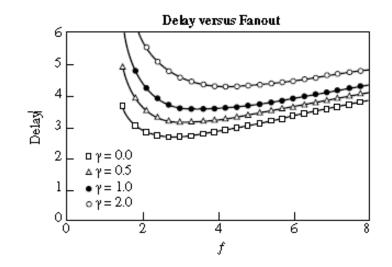

What *f* makes the total delay a minimum?

The optimum value of *f* depends on  $\gamma$  (for  $\gamma = 0$ , it is *e*).

It is similar calculation if we have chain of NAND and NORs:

$$\begin{aligned} \tau_{\text{rand}} &= R_{egn}C_{\text{in}} = R_{egn}\left(\frac{L_n}{W_n}\right) 4W_n C_g = 4R_{egn}C_g L_n \\ \tau_{\text{ror}} &= R_{egn}C_{\text{in}} = R_{egn}\left(\frac{L_n}{W_n}\right) 5W_n C_g = 5R_{egn}C_g L_n \end{aligned}$$

total\_delay =  $\sum_j \tau_{\text{rand}}\left(\frac{C_{j+1}}{C_j} + \gamma_{\text{rand}}\right)$

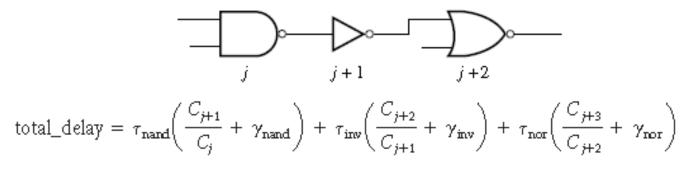

The delay through stages j and j + 1 is given by

$$D_{j+1} = \tau_{\text{nand}} \left( \frac{C_{j+1}}{C_j} + \gamma_{\text{nand}} \right) + \tau_{\text{inv}} \left( \frac{C_{j+2}}{C_{j+1}} + \gamma_{\text{inv}} \right)$$

For minimum delay, we take the derivative with respect to  $C_{j+1}$ :

$$\frac{\partial D_{j+1}}{\partial C_{j+1}} = \tau_{\text{nand}} \left( \frac{1}{C_j} \right) - \tau_{\text{inv}} \left( \frac{C_{j+2}}{C_{j+1}^2} \right) = 0$$

$$\therefore \tau_{\text{nand}} \left( \frac{C_{j+1}}{C_j} \right) = \tau_{\text{inv}} \left( \frac{C_{j+2}}{C_{j+1}} \right)$$

$$\therefore \tau_{\text{nand}} FO_j = \tau_{\text{inv}} FO_{j+1}$$

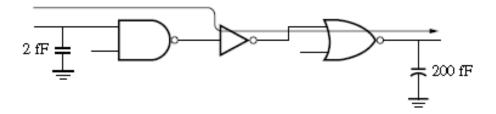

Example: Find the device sizes that optimize the delay through the indicated path for the circuit below.

We must equalize the fanout portion of the delay. Therefore,

$$\sim \tau_{\text{nand}} \left( \frac{C_{j+1}}{C_{\text{in}}} \right) = \tau_{\text{inv}} \left( \frac{C_{j+2}}{C_{j+1}} \right) = \tau_{\text{nor}} \left( \frac{C_{\text{load}}}{C_{j+2}} \right)$$

We take the product of these three components and then obtain the geometric mean:

$$\begin{aligned} \mathsf{Fanout\_delay} &= \sqrt[3]{\tau_{\mathsf{rand}} \left(\frac{C_{j+1}}{C_{\mathsf{in}}}\right) \times \tau_{\mathsf{inv}} \left(\frac{C_{j+2}}{C_{j+1}}\right) \times \tau_{\mathsf{nor}} \left(\frac{C_{\mathsf{load}}}{C_{j+2}}\right)} \\ &= \sqrt[3]{\tau_{\mathsf{rand}} \times \tau_{\mathsf{inv}} \times \tau_{\mathsf{nor}} \left(\frac{C_{\mathsf{load}}}{C_{\mathsf{in}}}\right)} = \sqrt[3]{4 \times 3 \times 5 \left(\frac{200}{2}\right) \times R_{\mathsf{eqn}} C_g L_p} \\ &= 18.2 R_{\mathsf{eqn}} C_g L_p \end{aligned}$$

Therefore, the input capacitance for each gate can be computed by setting the fanout delay to the above result:

$$\begin{aligned} \operatorname{fr}_{\operatorname{ror}}\left(\frac{C_{\operatorname{load}}}{C_{j+2}}\right) &= 5R_{\operatorname{eqn}}C_{g}L_{n}\left(\frac{200\ \operatorname{fF}}{C_{j+2}}\right) = 18.2\,R_{\operatorname{eqn}}C_{g}L_{n} \\ \therefore C_{j+2} &= 55\ \operatorname{fF} \\ \tau_{\operatorname{inv}} &= \left(\frac{C_{j+2}}{C_{j+1}}\right) = 3R_{\operatorname{eqn}}C_{g}L_{n}\left(\frac{55\ \operatorname{fF}}{C_{j+1}}\right) = 18.2\,R_{\operatorname{eqn}}C_{g}L_{n} \\ \therefore C_{j+1} &= 9.1\ \operatorname{fF} \\ \tau_{\operatorname{rand}}\left(\frac{C_{j+1}}{C_{\operatorname{in}}}\right) = 4\,R_{\operatorname{eqn}}C_{g}L_{n}\left(\frac{9.1\ \operatorname{fF}}{C_{\operatorname{in}}}\right) = 18.2\,R_{\operatorname{eqn}}C_{g}L_{n} \\ \therefore C_{\operatorname{in}} = 2\ \operatorname{fF} \end{aligned}$$