## EECE 488: Analog CMOS Integrated Circuit Design Assignment 2

Due: Thursday, March 1, 2012 at 9:30am

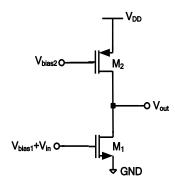

- **1.** Design a common-source amplifier with a current-source load based on the schematic shown below with the following design specifications:

- $V_{DD}=3V$

- Transistor  $M_1$  is in saturation

- The minimum possible output voltage to keep  $M_1$  in saturation is 0.1V

- The maximum possible output voltage to keep M<sub>2</sub> in saturation is 2.9V

- Total power consumption of the amplifier is 0.3mW

- L=0.4µm for the transistor

The technology parameters are:

$\lambda_{(NMOS)} = 0.1 V^{-1}, \ \lambda_{(PMOS)} = 0.2 V^{-1}, \ \gamma = 0, \ V_{DD} = 3V, \ V_{TH(NMOS)} = 0.5V, \ V_{TH(PMOS)} = -0.6V \\ \mu_n C_{ox} = 1 \ mA/V^2, \ \mu_p C_{ox} = 0.25 \ mA/V^2.$

Assuming both transistors are in saturation, find the following values:

(simplifying assumption: only use  $\lambda$  when calculating the output resistance of the transistors and ignore it for DC calculations.)

- a) DC level of the input, i.e.,  $V_{\text{bias1}}$

- b) V<sub>bias2</sub>

- c) Width (W<sub>1</sub>) of transistor M<sub>1</sub>

- d) Width (W<sub>2</sub>) of transistor M<sub>2</sub>

- e) Small-signal gain of the circuit

- f) Is the DC level of the output voltage well-defined?

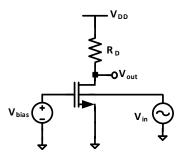

- 2. It is possible to use the <u>bulk terminal</u> of a transistor as an input of an amplifier. Consider the single-stage NMOS amplifier shown below. For  $V_{bias}=1.5V$ :

- a) What is the region of operation of the transistor?

- b) Calculate the small-signal gain ( $A_v = V_{out}/V_{in}$ ) of the amplifier. Recall that  $g_{mb} = \eta g_m$ . Assume,  $\lambda = 0$ ,  $\eta = 0.2$ ,  $V_{TH(NMOS)} = 0.5 V$ ,  $\mu_n C_{ox} = 100~\mu A/V^2$ ,  $R_D = 1 k\Omega$ , (W/L)<sub>NMOS</sub> = 20, and  $V_{DD} = 3 V$ . Note: In this problem, the technology parameters are different from those of Question 1.

- 3. Use HSPICE and our 0.35-µm CMOS technology to:

- a) Plot the intrinsic gain (i.e.,  $g_m r_o$ ) versus  $V_{DS}$  for an NMOS transistor of size W/L=3.5 $\mu$ m/0.35 $\mu$ m with a gate-source voltage of  $V_{GS}$ = $V_{th}$ +200mV.

- b) Repeat part a for an NMOS transistor of size W/L=14µm/1.4µm.

- c) Repeat parts a and b for a PMOS with  $V_{SG}=|V_{th}|+200mV$ .

Good luck!