## EECE488: Analog CMOS Integrated Circuit Design

### Introduction and Background

Shahriar Mirabbasi

Department of Electrical and Computer Engineering

University of British Columbia

shahriar@ece.ubc.ca

Technical contributions of Pedram Lajevardi in revising the slides is greatly acknowledged.

## Marking

Assignments 10% (4 to 6)

Midterm 15%

Project 25%

Final Exam 50%

### References

- Main reference: Lecture notes

- Recommended Textbook:

- Behzad Razavi, Design of Analog CMOS Integrated Circuits, McGraw-Hill, 2001

- Some other useful references:

- T. Chan Carusone, D. Johns and K. Martin, *Analog Integrated Circuit Design*, 2<sup>nd</sup> Edition, John Wiley, 2011

- P. Gray, P. Hurst, S. Lewis, and R. Meyer, *Analysis and Design of Analog Integrated Circuits*, 5<sup>th</sup> Edition, John Wiley, 2009

- D. Holberg and P. Allen, *CMOS Analog Circuit Design*, 3<sup>rd</sup> Edition, Oxford University Press, 2011

- R. Jacob Baker, CMOS Circuit Design, Layout, and Simulation, 3rd Edition, Wiley-IEEE Press, 2010

- A. Sedra and K.C. Smith, *Microelectronic Circuits*, 5<sup>th</sup> or 6<sup>th</sup> Edition, Oxford University Press, 2004, 2009

- Journal and conference articles including *IEEE Journal of Solid-State Circuits* and *International Solid-State Circuits Conference*

### Fun to Check

William F. Brinkman, Douglas E. Haggan, and William W. Troutman, "A History of the Invention of the Transistor and Where It Will Lead Us," *IEEE Journal of Solid-State Circuits*, volume 32, no. 12, December 1997, pp. 1858-1865

http://download.intel.com/newsroom/kits/22nm/pdfs/Intel\_Transistor\_Backgrounder.pdf

Boris Murmann, "Digitally Assisted Analog Circuits," IEEE Micro, vol. 26, no. 2, pp. 38-47, Mar. 2006.

Interesting CAD Tools by Dr. Michael Perrott and his group:

http://www.cppsim.com/download\_hspice\_tools.html

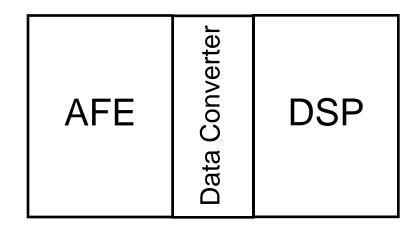

## Why Analog?

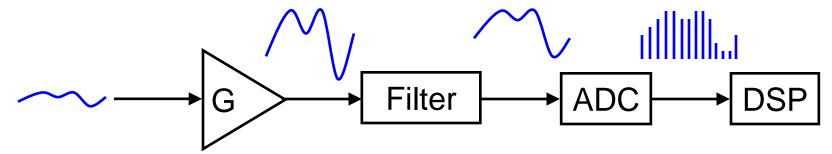

- Most of the physical signals are analog in nature!

- Although digital is great we need an analog interface to convert physical signals from analog to digital

- Also, in some application after processing the signals in digital domain, we need to convert them back to analog.

- Thus in many applications analog and mixed-signal circuits are the performance bottlenecks.

- Also with constant process improvements the boundary of between high-speed digital and analog circuits becomes more and more fuzzy!

- That is why analog and mixed-signal designers are still and hopefully will be in demand for the foreseeable future.

## Typical Real World System

Example:

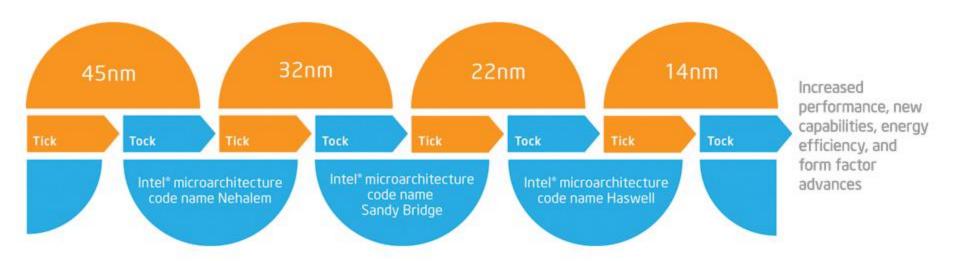

### Intel's Tick-Tock Model

# The Tick-Tock model through the years

Manufacturing process technology Microarchitectures

#### Tick (process technology advancement), Tock (new microarchitecture)

http://www.intel.com/content/www/us/en/silicon-innovations/intel-tick-tock-model-general.html

### Intel 45 nm Process

http://blog.oregonlive.com/siliconforest/2007/11/intel11.pdf

## Background

- 1. Suggested Reading

- 2. Structure of MOS Transistors

- 3. Threshold Voltage

- 4. Long-Channel Current Equations

- 5. Regions of Operation

- 6. Transconductance

- 7. Second-Order Effects

- 8. Short-Channel Effects

- 9. MOS Layout

- 10. Device Capacitances

- 11. Small-signal Models

- 12. Circuit Impedance

- 13. Equivalent Transconductance

## Suggested Reading

Most of the material in this set are based on

Chapters 2, 16, and 17 of the Razavi's book: Design of Analog CMOS Integrated Circuits

Many of the figures in this set are from © *Design of Analog CMOS Integrated Circuits*, McGraw-Hill, 2001, unless otherwise noted.

### **Transistor**

- Transistor stands for ...

- Transistor are semiconductor devices that can be classified as

- Bipolar Junction Transistors (BJTs)

- Field Effect Transistors (FETs)

- Depletion-Mode FETs or (e.g., JFETs)

Enhancement-Mode FETs (e.g., MOSFETs)

### Simplistic Model

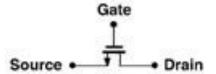

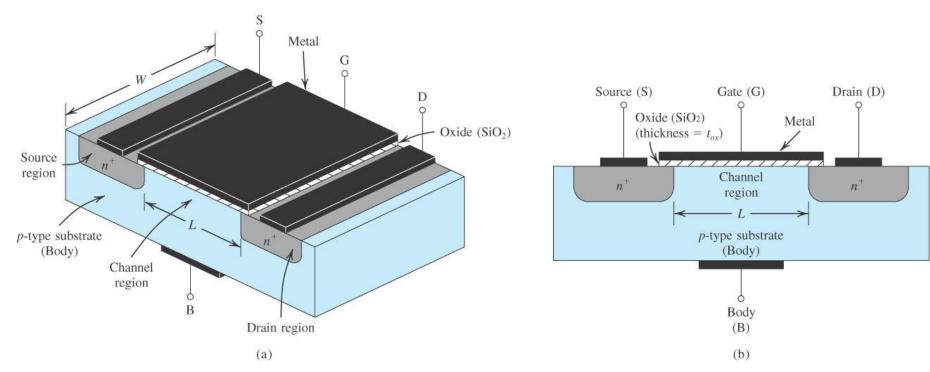

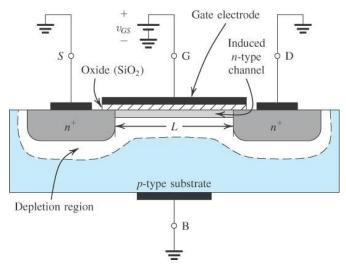

MOS transistors have three terminals: Gate, Source, and Drain

- The voltage of the Gate terminal determines the type of connection between Source and Drain (Short or Open).

- Thus, MOS devices behave like a switch

|                     | NMOS                   | PMOS                   |

|---------------------|------------------------|------------------------|

| V <sub>G</sub> high | Device is ON           | Device is OFF          |

|                     | D is shorted to S      | D & S are disconnected |

| V <sub>G</sub> low  | Device is OFF          | Device is ON           |

|                     | D & S are disconnected | D is shorted to S      |

- Source and Drain terminals are identical except that Source provides charge carriers, and Drain receives them.

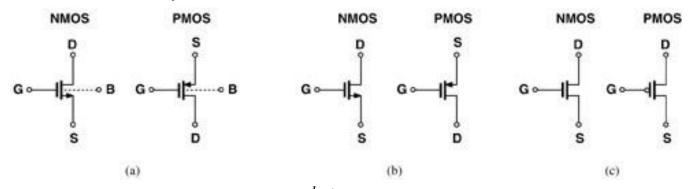

- MOS devices have in fact 4 terminals:

- Source, Drain, Gate, Substrate (bulk)

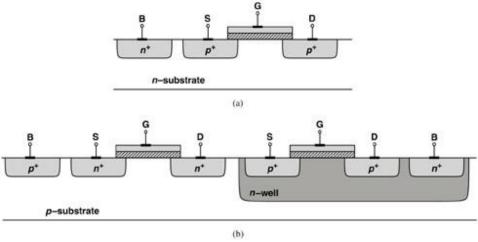

© Microelectronic Circuits, 2004 Oxford University Press

- Charge Carriers are electrons in NMOS devices, and holes in PMOS devices.

- Electrons have a higher mobility than holes

- So, NMOS devices are faster than PMOS devices

- We rather to have a p-type substrate?!

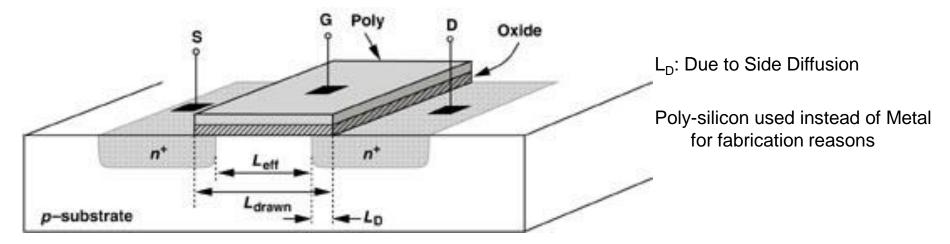

Actual length of the channel (L<sub>eff</sub>) is less than the length of gate

N-wells allow both NMOS and PMOS devices to reside on the same piece of die.

- As mentioned, NMOS and PMOS devices have 4 terminals:

Source, Drain, Gate, Substrate (bulk)

- In order to have all PN junctions reverse-biased, substrate of NMOS is connected to the most negative voltage, and substrate of PMOS is connected to the most positive voltage.

MOS transistor Symbols:

- In NMOS Devices: Source

<sup>electron</sup>→Drain

Current flows from Drain to Source

- In PMOS Devices:  $Source \xrightarrow{hole} Drain$ Current flows from Source to Drain

- Current flow determines which terminal is Source and which one is Drain. Equivalently, source and drain can be determined based on their relative voltages.

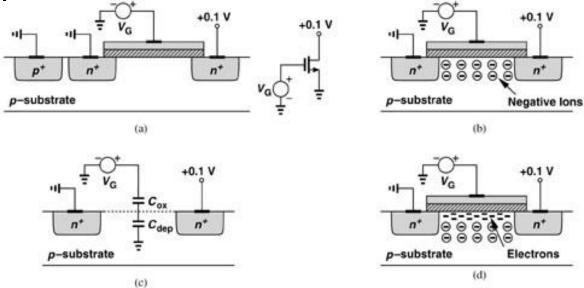

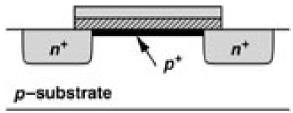

Consider an NMOS: as the gate voltage is increased, the surface under the gate is depleted. If the gate voltage increases more, free electrons appear under the gate and a conductive channel is formed.

- (a) An NMOS driven by a gate voltage, (b) formation of depletion region, (c) onset of inversion, and (d) channel formation

- As mentioned before, in NMOS devices charge carriers in the channel under the gate are electrons.

- Intuitively, the threshold voltage is the gate voltage that forces the interface (surface under the gate) to be completely depleted of charge (in NMOS the interface is as much n-type as the substrate is p-type)

- Increasing gate voltage above this threshold (denoted by V<sub>TH</sub> or V<sub>t</sub>) induces an inversion layer (conductive channel) under the gate.

© Microelectronic Circuits, 2004 Oxford University Press

### Analytically:

$$V_{TH} = \Phi_{MS} + 2 \cdot \left| \Phi_F \right| + \frac{\left| Q_{dep} \right|}{C_{ox}}$$

#### Where:

$\Phi_{MS} = \text{Built - in Potential } = \Phi_{gate} - \Phi_{Silicon}$

= the difference between the work functions of the polysilicon gate and the silicon substrate

$$\Phi_{F} = \text{Work Function (electrostatic potential)} = \frac{K \cdot T}{q} \cdot \ln \left( \frac{N_{sub}}{n_{i}} \right)$$

$$Q_{\tiny dep}$$

= Charge in the depletion region =  $\sqrt{4 \cdot q \cdot \varepsilon_{\tiny si} \cdot |\Phi_{\tiny F}| \cdot N_{\tiny sub}}$

- In practice, the "native" threshold value may not be suited for circuit design, e.g., V<sub>TH</sub> may be zero and the device may be on for any positive gate voltage.

- Typically threshold voltage is adjusted by ion implantation into the channel surface (doping P-type material will increase V<sub>TH</sub> of NMOS devices).

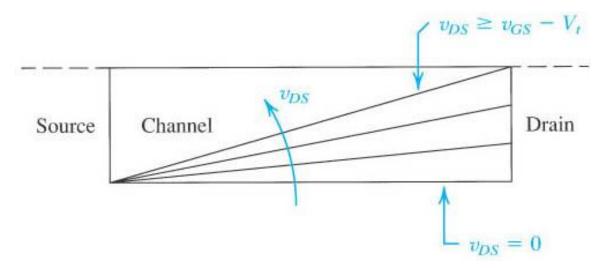

- When V<sub>DS</sub> is zero, there is no horizontal electric field present in the channel, and therefore no current between the source to the drain.

- When V<sub>DS</sub> is more than zero, there is some horizontal electric field which causes a flow of electrons from source to drain.

- The voltage of the surface under the gate, V(x), depends on the voltages of Source and Drain.

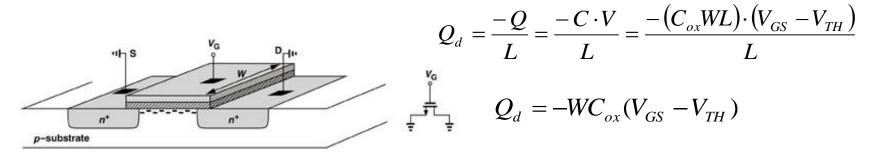

- If  $V_{DS}$  is zero,  $V_D = V_S = V(x)$ . The charge density  $Q_d$  (unit C/m) is uniform.

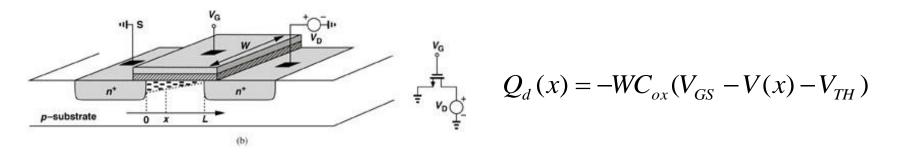

If V<sub>DS</sub> is not zero, the channel is tapered, and V(x) is not constant. The charge density depends on x.

Current :

$$I = \frac{dQ}{dt} = \frac{dQ}{dx} \times \frac{dx}{dt} = Q_d \cdot velocity$$

$\triangleright$  Velocity in terms of V(x):

velocity =

$$\mu \cdot E$$

,  $E = -\frac{dV}{dt}$

$$\rightarrow velocity = (\mu \cdot \frac{-dV(x)}{dx})$$

$\triangleright$  Q<sub>d</sub> in terms of V(x):

$$Q_d(x) = -WC_{ox}(V_{GS} - V(x) - V_{TH})$$

Current in terms of V(x):

$$\begin{split} I_{D} &= WC_{ox}[V_{GS} - V(x) - V_{TH}]\mu_{n} \frac{dV(x)}{dx} \\ \int\limits_{x=0}^{L} I_{D} dx &= \int\limits_{V=0}^{V_{DS}} WC_{ox} \mu_{n} [V_{GS} - V(x) - V_{TH}] dV \end{split}$$

Long-channel current equation:

$$I_D = \mu_n C_{ox} \frac{W}{L} [(V_{GS} - V_{TH})V_{DS} - \frac{1}{2}V_{DS}^2]$$

© Microelectronic Circuits, 2004 Oxford University Press

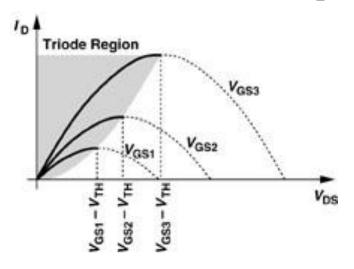

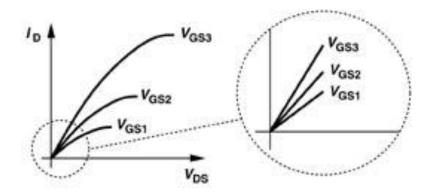

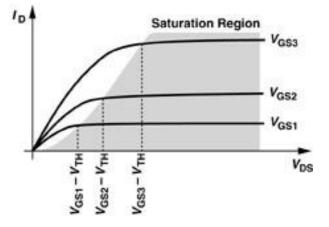

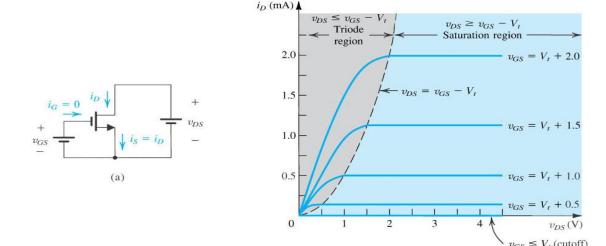

- If  $V_{DS} \le V_{GS} V_{TH}$  we say the device is operating in triode (or linear) region.

- Current in Triode Region:

$$I_D = \mu_n \cdot C_{ox} \cdot \frac{W}{L} \cdot \left[ \left( V_{GS} - V_{TH} \right) \cdot V_{DS} - \frac{1}{2} \cdot V_{DS}^2 \right]$$

Terminology:

$$Aspect \ Ratio = \frac{W}{L}$$

$Overdrive\ Voltage = Effective\ Voltage = V_{GS} - V_{TH} = V_{eff}$

For very small V<sub>DS</sub> (deep Triode Region):

$I_D$  can be approximated to be a linear function of  $V_{DS}$ .

The device resistance will be independent of  $V_{DS}$  and will only depend on  $V_{eff}$ .

The device will behave like a variable resistor

$$s \stackrel{\stackrel{G}{\longrightarrow}}{\longrightarrow} D \Leftrightarrow s \stackrel{V_{GS}}{\longrightarrow} D$$

If

$$V_{DS} \ll 2(V_{GS} - V_{TH})$$

:

$$I_D = \mu_n \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH}) \cdot V_{DS}$$

$$R_{ON} = \frac{V_{DS}}{I_D} = \frac{1}{\mu_n \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH})}$$

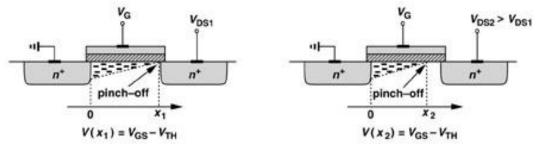

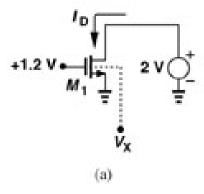

• Increasing  $V_{DS}$  causes the channel to acquire a tapered shape. Eventually, as  $V_{DS}$  reaches  $V_{GS} - V_{TH}$  the channel is pinched off at the drain. Increasing  $V_{DS}$  above  $V_{GS} - V_{TH}$  has little effect (ideally, no effect) on the channel's shape.

© Microelectronic Circuits, 2004 Oxford University Press

• When  $V_{DS}$  is more than  $V_{GS} - V_{TH}$  the channel is pinched off, and the horizontal electric field produces a current.

• If  $V_{DS} > V_{GS} - V_{TH}$ , the transistor is in saturation (active) region, and the channel is pinched off.

$$\int_{x=0}^{L'} I_D dx = \int_{V=0}^{V_{GS}-V_{TH}} WC_{ox} \mu_n [V_{GS} - V(x) - V_{TH}] dV$$

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L'} (V_{GS} - V_{TH})^2$$

Let's, for now, assume that L'=L. The fact that L' is not equal to L is a second-order effect known as channel-length modulation.

Since I<sub>D</sub> only depends on V<sub>GS</sub>, MOS transistors in saturation can be used as current sources.

Current Equation for NMOS:

$$I_{D} = I_{DS} = \begin{cases} 0 & ; if \ V_{GS} < V_{TH} \ (Cut - off) \\ \\ \mu_{n} \cdot C_{ox} \cdot \frac{W}{L} \cdot \left(V_{GS} - V_{TH}\right) \cdot V_{DS} & ; if \ V_{GS} > V_{TH} \ , V_{DS} << 2(V_{GS} - V_{TH}) \ (Deep \ Triode) \\ \\ \mu_{n} \cdot C_{ox} \cdot \frac{W}{L} \cdot \left(V_{GS} - V_{TH}\right) \cdot V_{DS} - \frac{1}{2} \cdot V_{DS}^{2} \right] & ; if \ V_{GS} > V_{TH} \ , V_{DS} < V_{GS} - V_{TH} \ (Triode) \\ \\ \frac{1}{2} \cdot \mu_{n} \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH})^{2} & ; if \ V_{GS} > V_{TH} \ , V_{DS} > V_{GS} - V_{TH} \ (Saturation) \end{cases}$$

Current Equation for PMOS:

$$I_{D} = I_{SD} = \begin{cases} 0 & ; if \ V_{SG} < \left|V_{TH}\right| \left(Cut - off\right) \\ \mu_{p} \cdot C_{ox} \cdot \frac{W}{L} \cdot \left(V_{SG} - \left|V_{TH}\right|\right) \cdot V_{SD} & ; if \ V_{SG} > \left|V_{TH}\right|, V_{SD} << 2(V_{SG} - \left|V_{TH}\right|) \ (Deep \ Triode) \\ \mu_{p} \cdot C_{ox} \cdot \frac{W}{L} \cdot \left[\left(V_{SG} - \left|V_{TH}\right|\right) \cdot V_{SD} - \frac{1}{2} \cdot V_{SD}^{2}\right] & ; if \ V_{SG} > \left|V_{TH}\right|, V_{SD} < V_{SG} - \left|V_{TH}\right| \ (Triode) \\ \frac{1}{2} \cdot \mu_{p} \cdot C_{ox} \cdot \frac{W}{L} \cdot \left(V_{SG} - \left|V_{TH}\right|\right)^{2} & ; if \ V_{SG} > \left|V_{TH}\right|, V_{SD} > V_{SG} - \left|V_{TH}\right| \ (Saturation) \end{cases}$$

Regions of Operation:

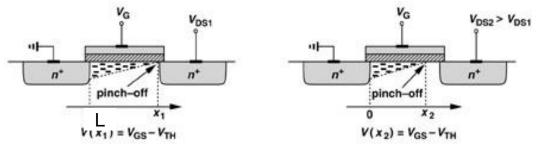

Cut-off, triode (linear), and saturation (active or pinch-off)

© Microelectronic Circuits, 2004 Oxford University Press

(b)

Once the channel is pinched off, the current through the channel is almost constant. As a result, the I-V curves have a very small slope in the pinch-off (saturation) region, indicating the large channel resistance.

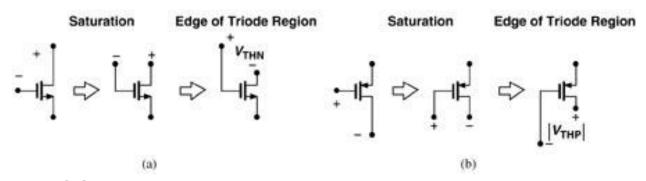

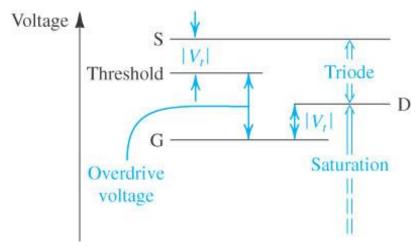

The following illustrates the transition from pinch-off to triode region for NMOS and PMOS devices.

- For NMOS devices:

- If  $V_D$  increases ( $V_G$  Const.), the device will go from Triode to Pinch-off. If  $V_G$  increases ( $V_D$  Const.), the device will go from Pinch-off to Triode.

- \*\* In NMOS, as V<sub>DG</sub> increases the device will go from Triode to Pinch-off.

- For PMOS devices:

- If  $V_D$  decreases ( $V_G$  Const.), the device will go from Triode to Pinch-off.

- If V<sub>G</sub> decreases (V<sub>D</sub> Const.), the device will go from Pinch-off to Triode.

- \*\* In PMOS, as V<sub>GD</sub> increases the device will go from Pinch-off to Triode.

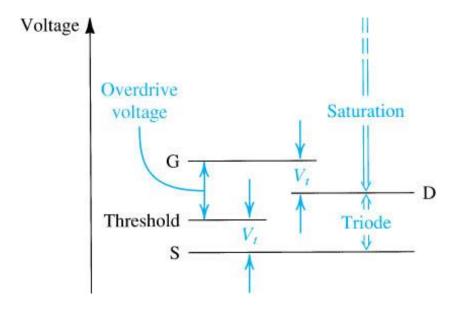

NMOS Regions of Operation:

© Microelectronic Circuits, 2004 Oxford University Press

Relative levels of the terminal voltages of the enhancement-type NMOS transistor for different regions of operation.

PMOS Regions of Operation:

© Microelectronic Circuits, 2004 Oxford University Press

The relative levels of the terminal voltages of the enhancement-type PMOS transistor for different regions of operation.

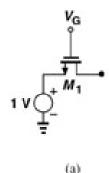

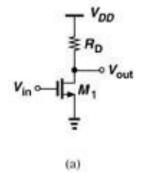

#### **Example:**

For the following circuit assume that  $V_{TH}=0.7V$ .

When is the device on?

What is the region of operation if the device is on?

Sketch the on-resistance of transistor M<sub>1</sub> as a function of V<sub>G</sub>.

### Transconductance - 1

- The drain current of the MOSFET in saturation region is ideally a function of gate-overdrive voltage (effective voltage). In reality, it is also a function of V<sub>DS</sub>.

- It makes sense to define a figure of merit that indicates how well the device converts the voltage to current.

- Which current are we talking about?

- What voltage is in the designer's control?

- What is this figure of merit?

$$g_m = \frac{\partial I_D}{\partial V_{GS}} \bigg|_{V_{DS}} = Const.$$

### Transconductance - 2

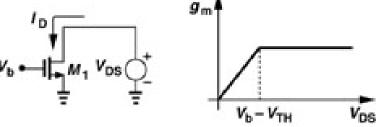

#### **Example:**

Plot the transconductance of the following circuit as a function of  $V_{DS}$  (assume  $V_b$  is a constant voltage).

Transconductance in triode:

$$g_{m} = \frac{\partial}{\partial V_{GS}} \left( \mu_{n} \cdot C_{ox} \cdot \frac{W}{L} \cdot \left[ \left( V_{GS} - V_{TH} \right) \cdot V_{DS} - \frac{1}{2} \cdot V_{DS}^{2} \right] \right) \Big|_{V_{DS}} = Const.$$

$$= \mu_{n} \cdot C_{ox} \cdot \frac{W}{L} \cdot V_{DS}$$

Transconductance in saturation:

$$g_{m} = \frac{\partial}{\partial V_{GS}} \left( \frac{1}{2} \cdot \mu_{n} \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH})^{2} \right) \Big|_{V_{DS}} = Const.$$

$$= \mu_{n} \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH})$$

Moral: Transconductance drops if the device enters the triode region.

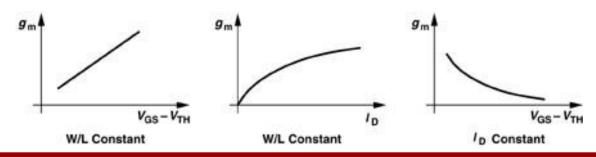

### Transconductance - 3

Transconductance, g<sub>m</sub>, in saturation:

$$g_m = \mu_n \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH}) = \sqrt{2\mu_n \cdot C_{ox} \cdot \frac{W}{L} \cdot I_D} = \frac{2 \cdot I_D}{V_{GS} - V_{TH}}$$

- If the aspect ratio is constant: g<sub>m</sub> depends linearly on (V<sub>GS</sub> V<sub>TH</sub>).

Also, g<sub>m</sub> depends on square root of I<sub>D</sub>.

- If I<sub>D</sub> is constant: g<sub>m</sub> is inversely proportional to (V<sub>GS</sub> V<sub>TH</sub>).

Also, g<sub>m</sub> depends on square root of the aspect ratio.

- If the overdrive voltage is constant: g<sub>m</sub> depends linearly on I<sub>D</sub>.

Also, g<sub>m</sub> depends linearly on the aspect ratio.

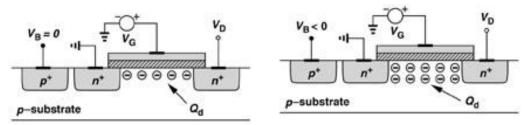

# Second-Order Effects (Body Effect)

### Substrate Voltage:

- So far, we assumed that the bulk and source of the transistor are at the same voltage (V<sub>B</sub>=V<sub>S</sub>).

- If V<sub>B</sub> > V<sub>s</sub>, then the bulk-source PN junction will be forward biased, and the device will not operate properly.

- If  $V_B < V_s$ ,

- the bulk-source PN junction will be reverse biased.

- the depletion region widens, and Q<sub>dep</sub> increases.

- V<sub>TH</sub> will be increased (Body effect or Backgate effect).

It can be shown that (what is the unit for γ?):

$$V_{TH} = V_{TH0} + \gamma \cdot \left( \sqrt{\left| 2 \cdot \Phi_F + V_{SB} \right|} - \sqrt{\left| 2 \cdot \Phi_F \right|} \right) \text{ where } \gamma = \frac{\sqrt{2 \cdot q \cdot \varepsilon_{si} \cdot N_{sub}}}{C_{ox}}$$

## Body Effect - 2

#### **Example:**

Consider the circuit below (assume the transistor is in the active region):

• If body-effect is ignored,  $V_{TH}$  will be constant, and  $I_1$  will only depend on  $V_{GS1}=V_{in}-V_{out}$ . Since  $I_1$  is constant,  $V_{in}-V_{out}$  remains constant.

$$V_{in} - V_{out} - V_{TH} = C = Const. \rightarrow V_{in} - V_{out} = V_{TH} + C = D = Conts.$$

• In general,  $I_1$  depends on  $V_{GS1}$ -  $V_{TH} = V_{in}$ - $V_{out}$ - $V_{TH}$  (and with body effect  $V_{TH}$  is not constant). Since  $I_1$  is constant,  $V_{in}$ - $V_{out}$ - $V_{TH}$  remains constant:

$$V_{in} - V_{out} - V_{TH} = C = Const. \rightarrow V_{in} - V_{out} = V_{TH} + C$$

• As  $V_{out}$  increases,  $V_{SB1}$  increases, and as a result  $V_{TH}$  increases. Therefore,  $V_{in}$ - $V_{out}$  Increases.

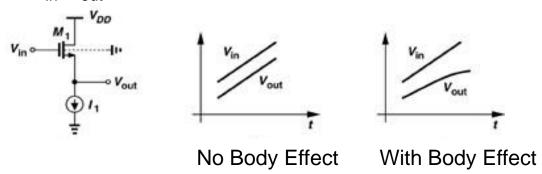

# Body Effect - 3

### **Example:**

For the following Circuit sketch the drain current of transistor  $M_1$  when  $V_X$  varies from  $-\infty$  to 0. Assume  $V_{TH0}=0.6V$ ,  $\gamma=0.4V^{1/2}$ , and  $2\Phi_F=0.7V$ .

# Channel Length Modulation - 1

• When a transistor is in the saturation region  $(V_{DS} > V_{GS} - V_{TH})$ , the channel is pinched off.

• The drain current is  $I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L'} (V_{GS} - V_{TH})^2$  where  $L' = L - \Delta L$

$$\frac{1}{L'} = \frac{1}{L - \Delta L} = \frac{1}{L} \cdot \frac{1}{1 - \Delta L/L} \approx \frac{1}{L} \cdot \left(1 + \frac{\Delta L}{L}\right)$$

- Assuming  $\Delta L/_{L} = \lambda \cdot V_{DS}$  we get:  $\frac{1}{L'} \approx \frac{1}{L} \cdot (1 + \Delta L/_{L}) = \frac{1}{L} \cdot (1 + \lambda \cdot V_{DS})$

- The drain current is  $I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L'} (V_{GS} V_{TH})^2 \approx \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} V_{TH})^2 \cdot (1 + \lambda \cdot V_{DS})$

- As I<sub>D</sub> actually depends on both V<sub>GS</sub> and V<sub>DS</sub>, MOS transistors are not ideal current sources (why?).

# Channel Length Modulation - 2

- $\lambda$  represents the relative variation in effective length of the channel for a given increment in  $V_{DS}$ .

- For longer channels λ is smaller, i.e., λ ∝ 1/L

- Transconductance:  $g_m = \frac{\partial I_D}{\partial V_{GS}} \Big|_{V_{DS} = Const.}$

In Triode:

$$g_m = \mu_n \cdot C_{ox} \cdot \frac{W}{L} \cdot V_{DS}$$

In Saturation (ignoring channel length modulation):

$$g_m = \mu_n \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH}) = \sqrt{2\mu_n \cdot C_{ox} \cdot \frac{W}{L} \cdot I_D} = \frac{2 \cdot I_D}{V_{GS} - V_{TH}}$$

In saturation with channel length modulation:

$$g_{m} = \mu_{n} \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH}) \cdot (1 + \lambda \cdot V_{DS}) = \sqrt{2\mu_{n} \cdot C_{ox} \cdot \frac{W}{L} \cdot I_{D} \cdot (1 + \lambda \cdot V_{DS})} = \frac{2 \cdot I_{D}}{V_{GS} - V_{TH}}$$

The dependence of I<sub>D</sub> on V<sub>DS</sub> is much weaker than its dependence on V<sub>GS</sub>.

# Channel Length Modulation - 3

### **Example:**

Given all other parameters constant, plot  $I_D$ - $V_{DS}$  characteristic of an NMOS for  $L=L_1$  and  $L=2L_1$

- In Triode Region:  $I_D \approx \mu_n \cdot C_{ox} \cdot \frac{W}{L} \cdot \left[ \left( V_{GS} V_{TH} \right) \cdot V_{DS} \frac{1}{2} \cdot V_{DS}^2 \right]$ Therefore :  $\frac{\partial I_D}{\partial V_{DS}} \propto \frac{W}{L}$

- In Saturation Region:  $I_D \approx \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} V_{TH})^2 \cdot (1 + \lambda \cdot V_{DS})$ So we get:  $\frac{\partial I_D}{\partial V_{DS}} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 \cdot \lambda$ Therefore:  $\frac{\partial I_D}{\partial V_{DS}} \propto \frac{W \cdot \lambda}{L} \propto \frac{W}{L^2}$

- Changing the length of the device from L<sub>1</sub> to 2L<sub>1</sub> will flatten the I<sub>D</sub>-V<sub>DS</sub> curves (slope will be divided by two in triode and by four in saturation).

- Increasing L will make a transistor a better current source, while degrading its current capability.

- Increasing W will improve the current capability.

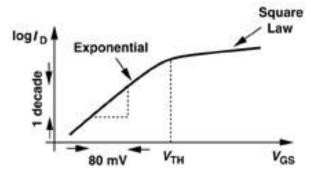

### **Sub-threshold Conduction**

- If V<sub>GS</sub> < V<sub>TH</sub>, the drain current is not zero.

- The MOS transistors behave similar to BJTs.

• In BJT:

$$I_C = I_S \cdot e^{\frac{V_{BE}}{V_T}}$$

• In MOS:

$$I_D = I_0 \cdot e^{\frac{V_{GS}}{\zeta \cdot V_T}}$$

- As shown in the figure, in MOS transistors, the drain current drops by one decade for approximately each 80mV of drop in V<sub>GS</sub>.

- In BJT devices the current drops faster (one decade for approximately each 60mv of drop in V<sub>GS</sub>).

- This current is known as sub-threshold or weak-inversion conduction.

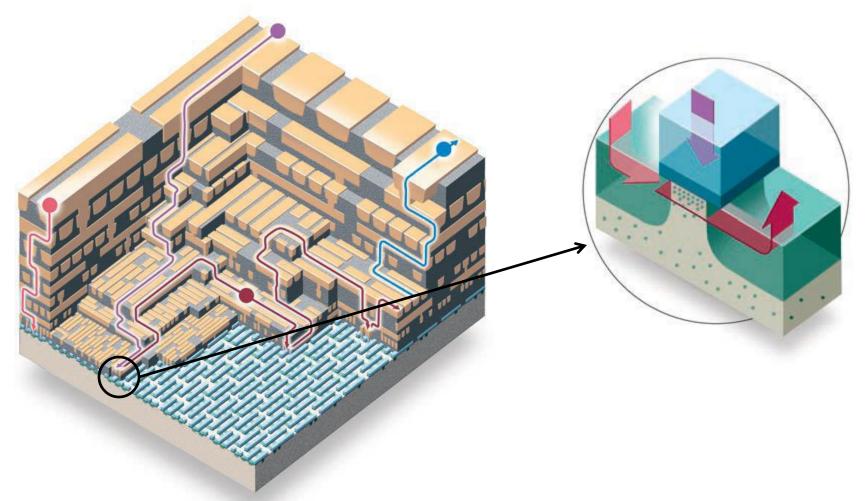

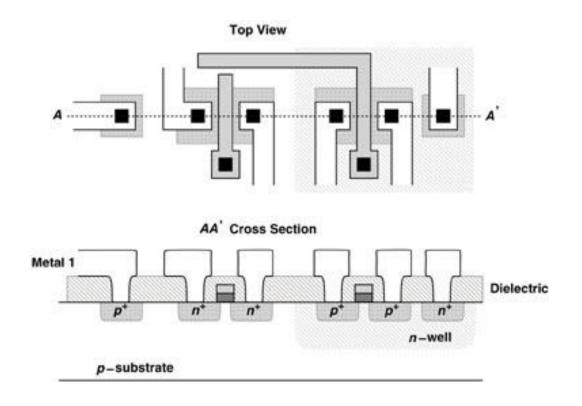

# **CMOS** Processing Technology

Top and side views of a typical CMOS process

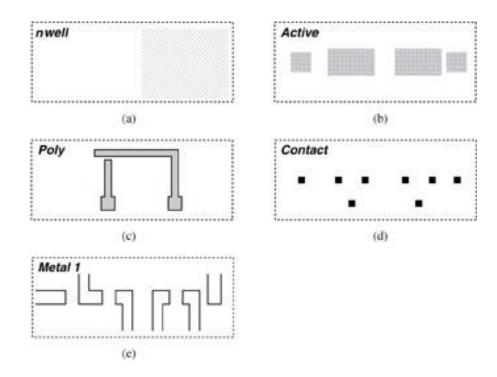

# **CMOS** Processing Technology

Different layers comprising CMOS transistors

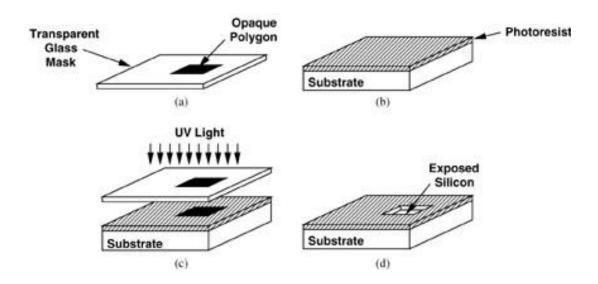

# Photolithography (Lithography)

Used to transfer circuit layout information to the wafer

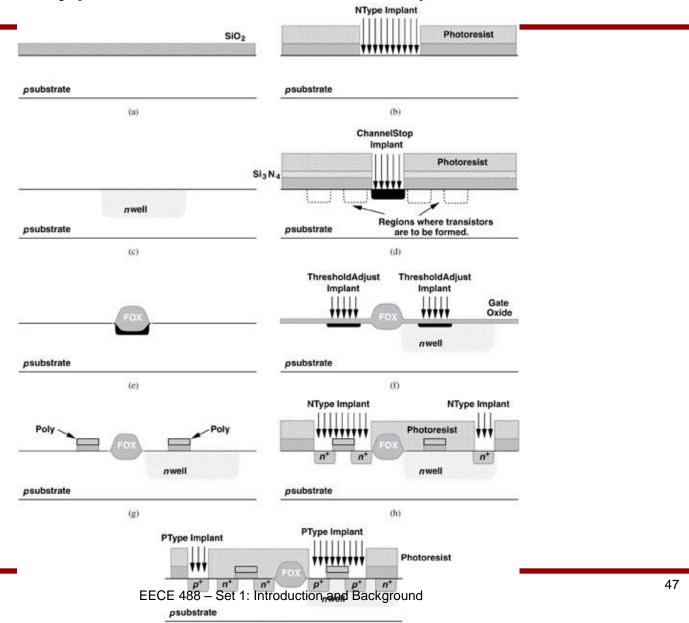

# Typical Fabrication Sequence

(i)

SM

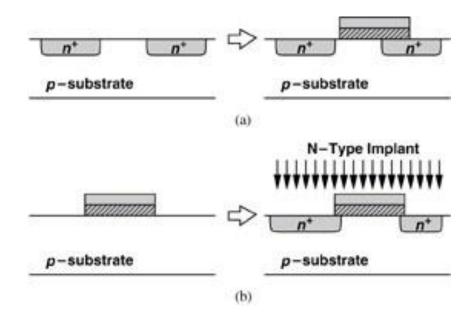

# **Self-Aligned Process**

Why source and drain junctions are formed after the gate oxide and polysilicon layers are deposited?

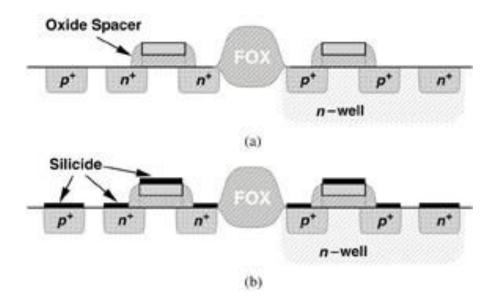

# **Back-End Processing**

Oxide spacers and silicide

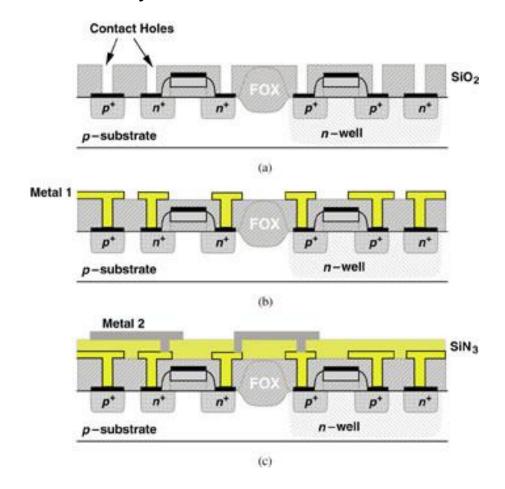

# **Back-End Processing**

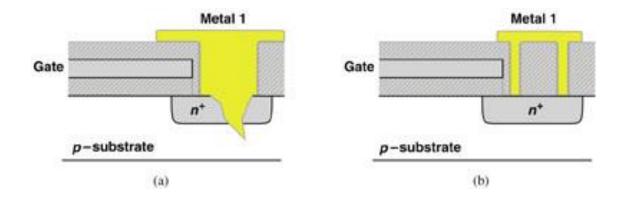

Contact and metal layers fabrication

# **Back-End Processing**

Large contact areas should be avoided to minimize the possibility of spiking

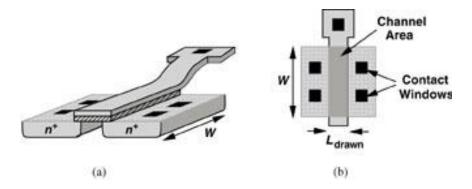

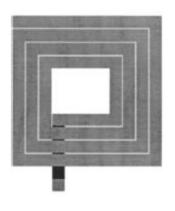

# MOS Layout - 1

It is beneficial to have some insight into the layout of the MOS devices.

- When laying out a design, there are many important parameters we need to pay attention to such as: drain and source areas, interconnects, and their connections to the silicon through contact windows.

- Design rules determine the criteria that a circuit layout must meet for a given technology. Things like, minimum length of transistors, minimum area of contact windows, ...

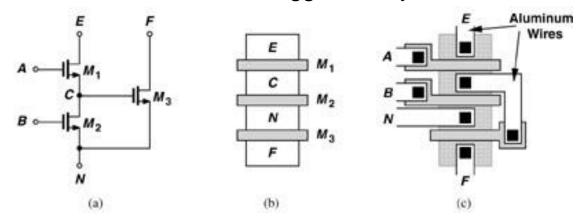

# MOS Layout - 2

### **Example:**

Figures below show a circuit with a suggested layout.

The same circuit can be laid out in different ways, producing different electrical parameters (such as different terminal capacitances).

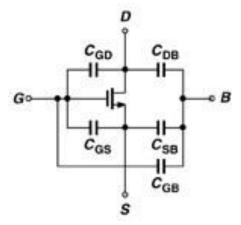

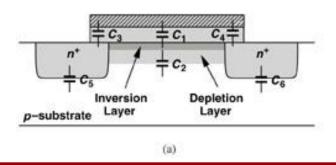

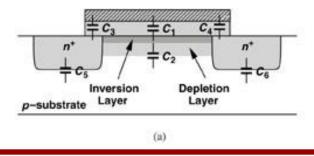

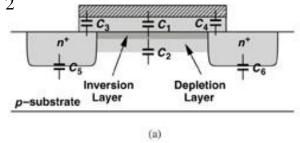

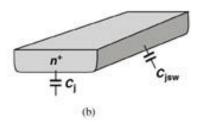

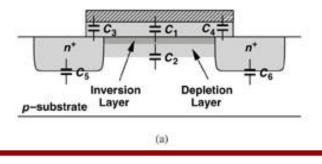

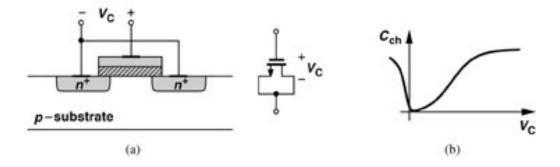

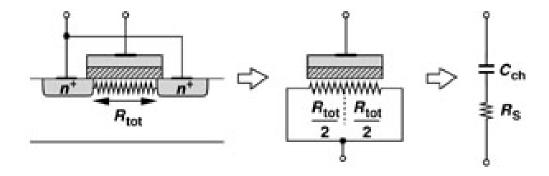

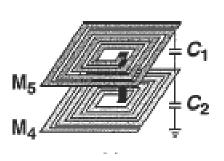

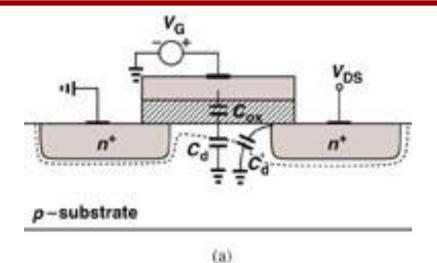

- The quadratic model determines the DC behavior of a MOS transistor.

- The capacitances associated with the devices are important when studying the AC behavior of a device.

- There is a capacitance between any two terminals of a MOS transistor.

So there are 6 Capacitances in total.

- The Capacitance between Drain and Source is negligible (C<sub>DS</sub>=0).

These capacitances will depend on the region of operation (Bias values).

- The following will be used to calculate the capacitances between terminals:

- 1. Oxide Capacitance:  $C_1 = W \cdot L \cdot C_{ox}$ ,  $C_{ox} = \frac{\mathcal{E}_{ox}}{t_{ox}}$

- 2. Depletion Capacitance:  $C_2 = C_{dep} = W \cdot L \cdot \sqrt{\frac{q \cdot \varepsilon_{si} \cdot N_{sub}}{4 \cdot \Phi_F}}$

- 3. Overlap Capacitance:  $C_3 = C_4 = C_{ov} = W \cdot L_D \cdot C_{ox} + C_{fringe}$

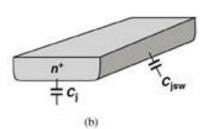

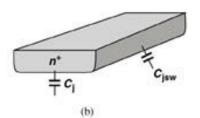

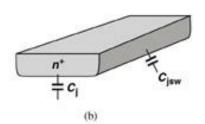

- 4. Junction Capacitance:

- ➤ Sidewall Capacitance: C<sub>jsw</sub>

- ➤ Bottom-plate Capacitance: *c*,

$$C_5 = C_6 = C_i + C_{isw}$$

#### In Cut-off:

- 1.  $C_{GS}$ : is equal to the overlap capacitance.  $C_{GS} = C_{ov} = C_3$

- 2.  $C_{GD}$ : is equal to the overlap capacitance.  $C_{GD} = C_{ov} = C_4$

- 3.  $C_{GB}$ : is equal to  $C_{gate-channel} = C_1$  in series with  $C_{channel-bulk} = C_2$ .

- 4. C<sub>SB</sub>: is equal to the junction capacitance between source and bulk.

- 5. C<sub>DB</sub>: is equal to the junction capacitance between source and bulk.

$$C_{SB} = C_5$$

$$C_{DB} = C_6$$

#### In Triode:

The channel isolates the gate from the substrate. This means that if V<sub>G</sub> changes, the charge of the inversion layer are supplied by the drain and source as long as V<sub>DS</sub> is close to zero. So, C<sub>1</sub> is divided between gate and drain terminals, and gate and source terminals, and C<sub>2</sub> is divided between bulk and drain terminals, and bulk and source terminals.

1.

$$C_{GS}$$

:  $C_{GS} = C_{ov} + \frac{C_1}{2}$

2.

$$C_{GD}$$

:  $C_{GD} = C_{ov} + \frac{C_1}{2}$

3.  $C_{GB}$ : the channel isolates the gate from the substrate.  $C_{GB} = 0$

4.

$$C_{SB}$$

:  $C_{SB} = C_5 + \frac{C_2}{2}$

4.

$$C_{SB}$$

:  $C_{SB} = C_5 + \frac{C_2}{2}$

5.  $C_{DB}$ :  $C_{DB} = C_6 + \frac{C_2}{2}$

#### In Saturation:

The channel isolates the gate from the substrate. The voltage across the channel varies which can be accounted for by adding two equivalent capacitances to the source. One is between source and gate, and is equal to two thirds of C<sub>1</sub>. The other is between source and bulk, and is equal to two thirds of  $C_2$ .

1.

$$C_{GS}$$

:  $C_{GS} = C_{ov} + \frac{2}{3}C_1$

2.

$$C_{GD}$$

:  $C_{GD} = C_{ov}$

3.  $C_{GB}$ : the channel isolates the gate from the substrate.  $C_{GB} = 0$

4.

$$C_{SB}$$

:  $C_{SB} = C_5 + \frac{2}{3}C_2$

5.  $C_{DB}$ :  $C_{DB} = C_6$

5.

$$C_{DB}$$

:  $C_{DB} = C_6$

### In summary:

|                 | Cut-off                                                      | Triode                   | Saturation                |

|-----------------|--------------------------------------------------------------|--------------------------|---------------------------|

| C <sub>GS</sub> | $C_{ov}$                                                     | $C_{ov} + \frac{C_1}{2}$ | $C_{ov} + \frac{2}{3}C_1$ |

| $C_{\sf GD}$    | $C_{ov}$                                                     | $C_{ov} + \frac{C_1}{2}$ | $C_{ov}$                  |

| $C_{GB}$        | $\frac{C_1 \cdot C_2}{C_1 + C_2} \langle C_{GB} \langle C_1$ | 0                        | 0                         |

| C <sub>SB</sub> | $C_5$                                                        | $C_5 + \frac{C_2}{2}$    | $C_5 + \frac{2}{3}C_2$    |

| C <sub>DB</sub> | $C_6$                                                        | $C_6 + \frac{C_2}{2}$    | $C_6$                     |

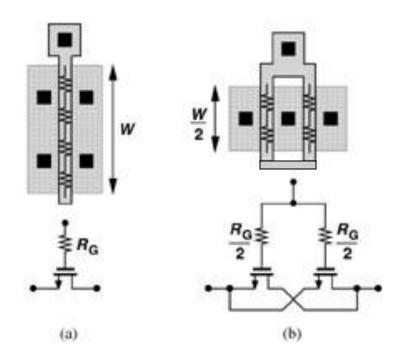

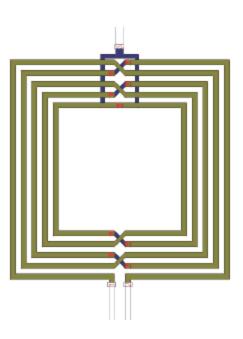

# Importance of Layout

### **Example (Folded Structure):**

Calculate the gate resistance of the circuits shown below.

#### Folded structure:

- Decreases the drain capacitance

- Decreases the gate resistance

- Keeps the aspect ratio the same

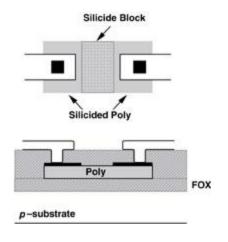

### Resistors

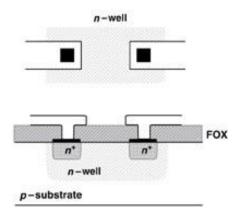

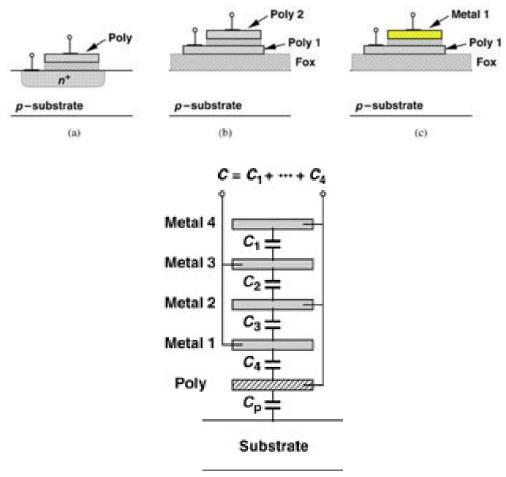

### Capacitors:

SM

### Capacitors

### Inductors

# Latch-Up

Due to parasitic bipolar transistors in a CMOS process

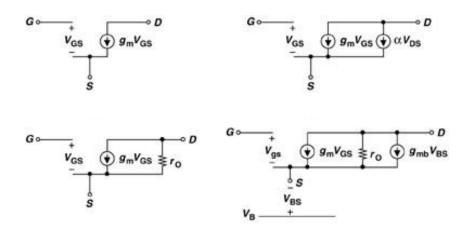

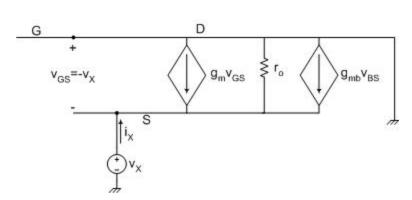

- Small signal model is an approximation of the large-signal model around the operation point.

- In analog circuits most MOS transistors are biased in saturation region.

- In general,  $I_D$  is a function of  $V_{GS}$ ,  $V_{DS}$ , and  $V_{BS}$ . We can use this Taylor series approximation:

$$\begin{split} & \text{Tay lor Expansion}: I_{D} = I_{D0} + \frac{\partial I_{D}}{\partial V_{GS}} \cdot \Delta V_{GS} + \frac{\partial I_{D}}{\partial V_{DS}} \cdot \Delta V_{DS} + \frac{\partial I_{D}}{\partial V_{BS}} \cdot \Delta V_{BS} + \text{second order terms} \\ & \Delta I_{D} \approx \frac{\partial I_{D}}{\partial V_{GS}} \cdot \Delta V_{GS} + \frac{\partial I_{D}}{\partial V_{DS}} \cdot \Delta V_{DS} + \frac{\partial I_{D}}{\partial V_{BS}} \cdot \Delta V_{BS} = g_{m} \cdot \Delta V_{GS} + \frac{\Delta V_{DS}}{r_{o}} + g_{mb} \cdot \Delta V_{BS} \end{split}$$

- Current in Saturation:  $I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L'} (V_{GS} V_{TH})^2 \approx \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} V_{TH})^2 \cdot (1 + \lambda \cdot V_{DS})$

- Taylor approximation:  $\Delta I_D \approx \frac{\partial I_D}{\partial V_{GS}} \cdot \Delta V_{GS} + \frac{\partial I_D}{\partial V_{DS}} \cdot \Delta V_{DS} + \frac{\partial I_D}{\partial V_{BS}} \cdot \Delta V_{BS}$

- Partial Derivatives:

$$\begin{split} \frac{\partial I_{D}}{\partial V_{GS}} &= \mu_{n} \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH}) \cdot (1 + \lambda \cdot V_{DS}) = g_{m} \\ \frac{\partial I_{D}}{\partial V_{DS}} &= \frac{1}{2} \cdot \mu_{n} \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH})^{2} \cdot \lambda \approx I_{D} \cdot \lambda = \frac{1}{r_{o}} \\ \frac{\partial I_{D}}{\partial V_{BS}} &= \frac{\partial I_{D}}{\partial V_{TH}} \cdot \frac{\partial V_{TH}}{\partial V_{BS}} = \left[ -\mu_{n} \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH}) \cdot (1 + \lambda \cdot V_{DS}) \right] \cdot \left[ -\frac{\gamma}{2\sqrt{|2 \cdot \Phi_{F} + V_{SB}|}} \right] \\ &= -g_{m} \cdot \left[ -\frac{\gamma}{2\sqrt{|2 \cdot \Phi_{F} + V_{SB}|}} \right] = g_{m} \cdot \eta = g_{mb} \end{split}$$

Small-Signal Model:

$$i_D = g_m \cdot v_{GS} + \frac{v_{DS}}{r_o} + g_{mb} \cdot v_{BS}$$

- Terms,  $g_m v_{GS}$  and  $g_{mb} v_{BS}$ , can be modeled by dependent sources. These terms have the same polarity: increasing  $v_G$ , has the same effect as increasing  $v_B$ .

- The term, v<sub>DS</sub>/r<sub>o</sub> can be modeled using a resistor as shown below.

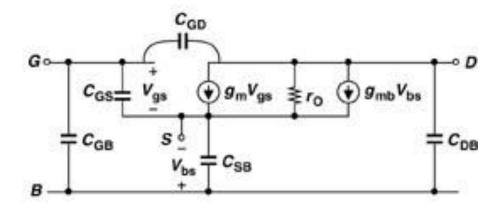

Complete Small-Signal Model with Capacitances:

- Small signal model including all the capacitance makes the intuitive (qualitative) analysis of even a few-transistor circuit difficult!

- Typically, CAD tools are used for accurate circuit analysis

- For intuitive analysis we try to find a simplest model that can represent the role of each transistor with reasonable accuracy.

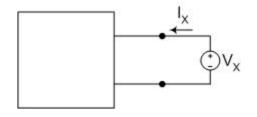

# Circuit Impedance - 1

- It is often useful to determine the impedance of a circuit seen from a specific pair of terminals.

- The following is the recipe to do so:

- 1. Connect a voltage source,  $V_X$ , to the port.

- 2. Suppress all independent sources.

- 3. Measure or calculate  $I_x$ .

$$R_{X} = \frac{V_{X}}{I_{X}}$$

# Circuit Impedance - 2

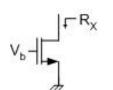

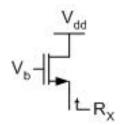

#### **Example:**

- Find the small-signal impedance of the following current sources.

- $V_b = \begin{bmatrix} V_{dd} \\ V_b \end{bmatrix}$

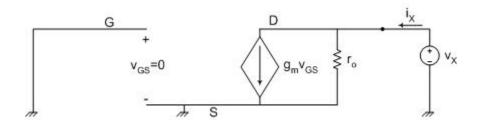

- We draw the small-signal model, which is the same for both circuits, and connect a voltage source as shown below:

$$i_{x} = \frac{v_{x}}{r_{o}} + g_{m} \cdot v_{GS} = \frac{v_{x}}{r_{o}}$$

$$R_{X} = \frac{v_{X}}{i_{X}} = r_{o}$$

# Circuit Impedance - 3

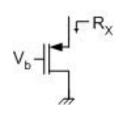

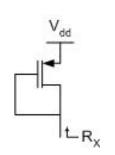

#### **Example:**

- Find the small-signal impedance of the following circuits.

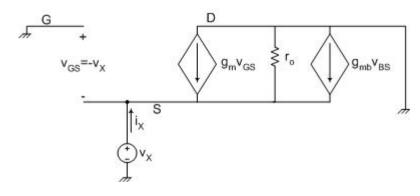

- We draw the small-signal model, which is the same for both circuits, and connect a voltage source as shown below:

$$i_{X} = \frac{V_{X}}{r_{o}} - g_{m} \cdot V_{GS} - g_{mb} \cdot V_{BS} = \frac{V_{X}}{r_{o}} + g_{m} \cdot V_{X} + g_{mb} \cdot V_{X}$$

$$R_{x} = \frac{v_{x}}{i_{x}} = \frac{1}{\frac{1}{r_{o}} + g_{m} + g_{mb}} = r_{o} \left\| \frac{1}{g_{m}} \right\| \frac{1}{g_{mb}}$$

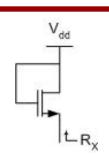

# Circuit Impedance - 4

#### **Example:**

Find the small-signal impedance of the following circuit. This

circuit is known as the diode-connected load, and is used

frequently in analog circuits.

We draw the small-signal model and connect the voltage source as shown below:

$$i_{x} = \frac{v_{x}}{r_{o}} + g_{m} \cdot v_{GS} = \frac{v_{x}}{r_{o}} + g_{m} \cdot v_{x} = v_{x} \cdot \left(\frac{1}{r_{o}} + g_{m}\right)$$

$$R_{x} = \frac{v_{x}}{i_{x}} = \frac{1}{1 + g_{m}} = r_{o} \left\| \frac{1}{g_{m}} \right\|$$

$$G \downarrow V_{GS} = v_{x}$$

$$V_{GS} = v_{x}$$

$$V_{GS} = v_{x}$$

$$V_{GS} = v_{x}$$

If channel length modulation is ignored (r<sub>o</sub>=∞) we get:

$$R_{X} = r_{o} \left\| \frac{1}{g_{m}} = \infty \right\| \frac{1}{g_{m}} = \frac{1}{g_{m}}$$

# Circuit Impedance - 5

#### **Example:**

Find the small-signal impedance of the following circuit. This

circuit is a diode-connected load with body effect.

$$i_{X} = \frac{v_{X}}{r_{o}} - g_{m} \cdot v_{GS} - g_{mb} \cdot v_{BS} = \frac{v_{X}}{r_{o}} + g_{m} \cdot v_{X} + g_{mb} \cdot v_{X}$$

$$= v_{X} \cdot \left(\frac{1}{r_{o}} + g_{m} + g_{mb}\right)$$

$$R_{x} = \frac{v_{x}}{i_{x}} = \frac{1}{\frac{1}{r} + g_{m} + g_{mb}} = r_{o} \left\| \frac{1}{g_{m} + g_{mb}} = r_{o} \right\| \frac{1}{g_{m}} \left\| \frac{1}{g_{mb}} \right\|$$

• If channel length modulation is ignored  $(r_o=\infty)$  we get:

$$R_{x} = r_{o} \left\| \frac{1}{g_{m} + g_{mb}} = \infty \right\| \frac{1}{g_{m} + g_{mb}} = \frac{1}{g_{m} + g_{mb}} = \frac{1}{g_{m}} \left\| \frac{1}{g_{mb}} \right\|$$

## **Equivalent Transconductance - 1**

Recall that the transconductance of a transistor was a a figure of merit that indicates how well the device converts a voltage to current.

$$g_{m} = \frac{\partial I_{D}}{\partial V_{GS}} \Big|_{V_{DS}} = Const.$$

It is sometimes useful to define the equivalent transconductance of a circuit as follows:

$$G_{m} = \frac{\partial I_{OUT}}{\partial V_{N}} \Big|_{V_{OUT}} = Const.$$

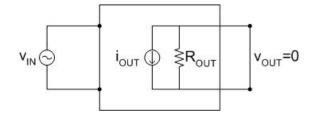

The following is a small-signal block diagram of an arbitrary circuit with a Norton equivalent at the output port. We notice that: V<sub>OUT</sub>=Constant so v<sub>OUT</sub>=0 in the small signal model.

$$G_{\scriptscriptstyle m} = \frac{i_{\scriptscriptstyle OUT}}{v_{\scriptscriptstyle IN}} \bigg|_{v_{\scriptscriptstyle OUT}} = 0$$

## Equivalent Transconductance - 2

### **Example:**

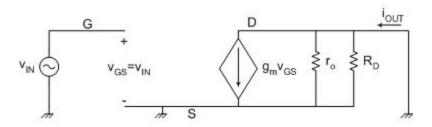

Find the equivalent transconductance of an NMOS transistor in saturation from its small-signal model.

$$i_{\scriptscriptstyle OUT} = g_{\scriptscriptstyle m} \cdot v_{\scriptscriptstyle GS} = g_{\scriptscriptstyle m} \cdot v_{\scriptscriptstyle IN}$$

$G_{\scriptscriptstyle m} = \frac{i_{\scriptscriptstyle OUT}}{v_{\scriptscriptstyle IN}} = g_{\scriptscriptstyle m}$

## Equivalent Transconductance - 3

#### **Example:**

Find the equivalent transconductance of the following circuit when the NMOS transistor in saturation.

$$\begin{aligned} v_{IN} &= v_{GS} + v_{S} = v_{GS} + i_{OUT} \cdot R_{S} \\ i_{OUT} &= g_{IM} \cdot v_{GS} + g_{IM} \cdot v_{IS} - \frac{v_{S}}{r_{O}} = g_{IM} \cdot (v_{IN} - i_{OUT} \cdot R_{S}) + g_{IM} \cdot (-i_{OUT} \cdot R_{S}) - \frac{i_{OUT} \cdot R_{S}}{r_{O}} \\ i_{OUT} \cdot \left(1 + g_{IM} \cdot R_{S} + g_{IM} \cdot R_{S} + \frac{R_{S}}{r_{O}}\right) = g_{IM} \cdot v_{IN} \\ G_{IM} &= \frac{i_{OUT}}{v_{IN}} = \frac{g_{IM}}{1 + g_{IM} \cdot R_{S} + g_{IM}} \cdot R_{S} + \frac{R_{S}}{r_{O}} = \frac{g_{IM} \cdot r_{O}}{r_{O} + r_{O} \cdot (g_{IM} \cdot R_{S} + g_{IM} \cdot R_{S}) + R_{S}} \end{aligned}$$

### **Short-Channel Effects**

- Threshold Reduction

- Drain-induced barrier lowering (DIBL)

- Mobility degradation

- Velocity saturation

- Hot carrier effects

- Substrate current

- Gate current

- Output impedance variation

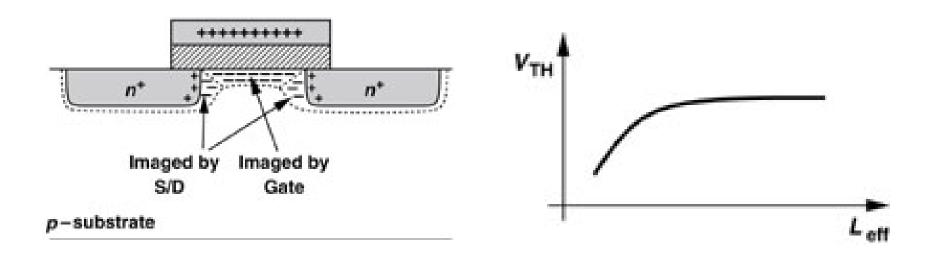

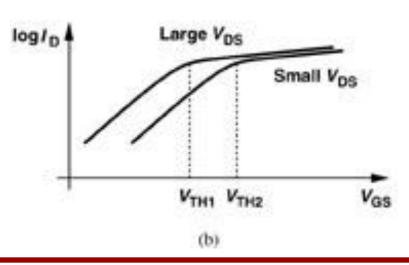

### Threshold Voltage Variation in Short Channel Devices

• The Threshold of transistors fabricated on the same chip decreases as the channel length decreases.

Intuitively, the extent of depletion regions associated with drain and source in the channel area, reduces the immobile charge that must be imaged by the charge on the gate.

## Drain-Induced Barrier Lowering (DIBL)

When the channel is short, the drain voltage increases the channel surface potential, lowering the barrier to flow charge from source (think of increased electric field) and therefore, decreasing the threshold.

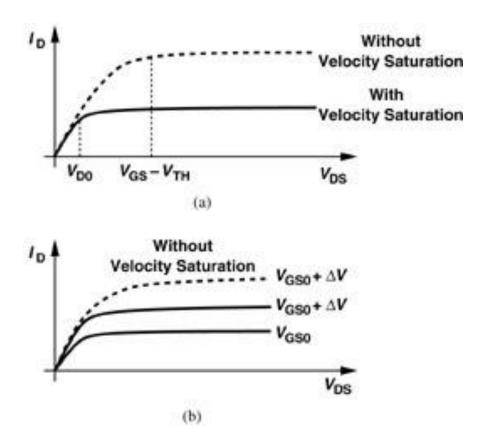

# Effects of Velocity Saturation

Due to drop in mobility at high electric fields

(a) Premature drain current saturation and (b) reduction in g<sub>m</sub>

### **Hot Carrier Effects**

- Short channel devices may experience high lateral drain-source electric field

- Some carriers that make it to drain have high velocity (called "hot" carriers)

- "Hot" carriers may "hit" silicon atoms at high speed and cause impact ionization

- The resulting electron and holes are absorbed by the drain and substrate causing extra drain-substrate current

- Really "hot" carriers may be injected into gate oxide and flow out of gate causing gate current!

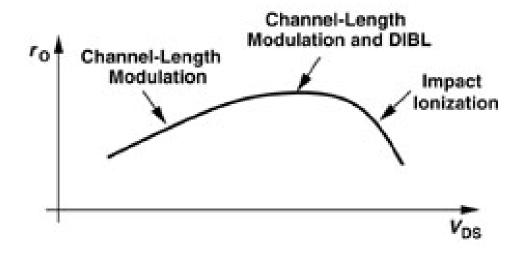

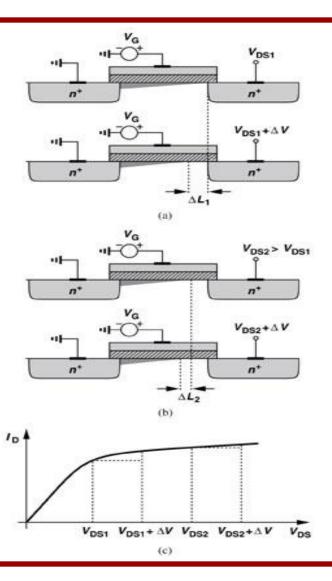

# **Output Impedance Variation**

#### Recall the definition of $\lambda$ .

### Output Impedance Variation in Short-Channel Devices