#### EECE488: Analog CMOS Integrated Circuit Design

Set 5

#### **Current Mirrors**

Shahriar Mirabbasi

Department of Electrical and Computer Engineering

University of British Columbia

shahriar@ece.ubc.ca

# **Applications of Current Sources**

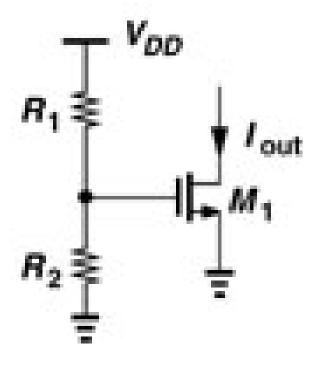

## Simple Resistive Biasing for Current Source

$$I_{OUT} \approx \frac{\mu_n C_{ox}}{2} \frac{W}{L} \left( \frac{R_2}{R_2 + R_1} V_{DD} - V_{TH} \right)^2$$

#### **Problems**

- Output current depends on:

- Supply

- Process

- Temperature

- What if the bias voltage is independent of supply voltage?

- Is there a way of generating reliable currents?

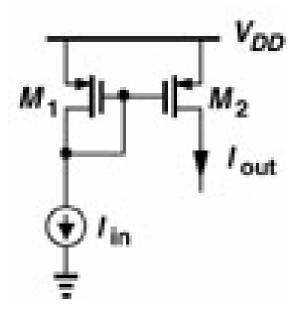

#### Basic Idea

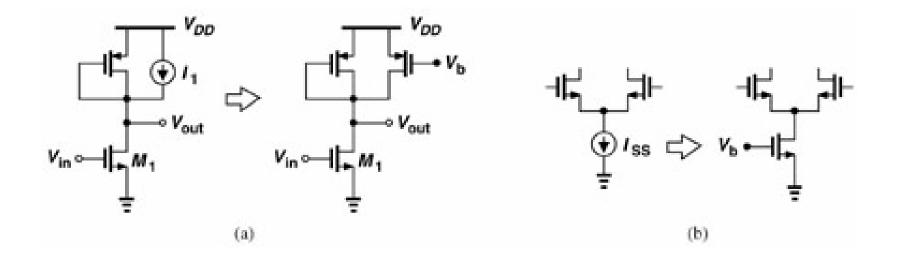

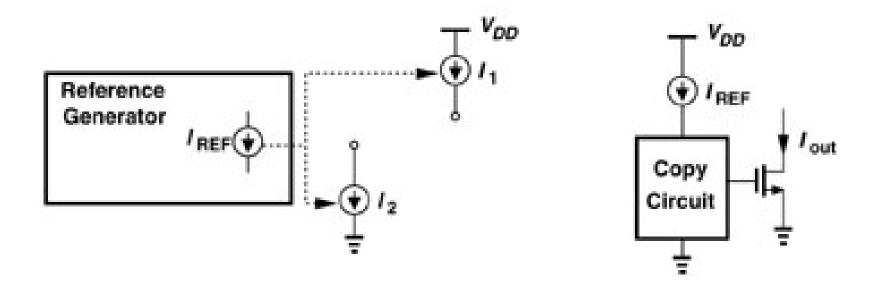

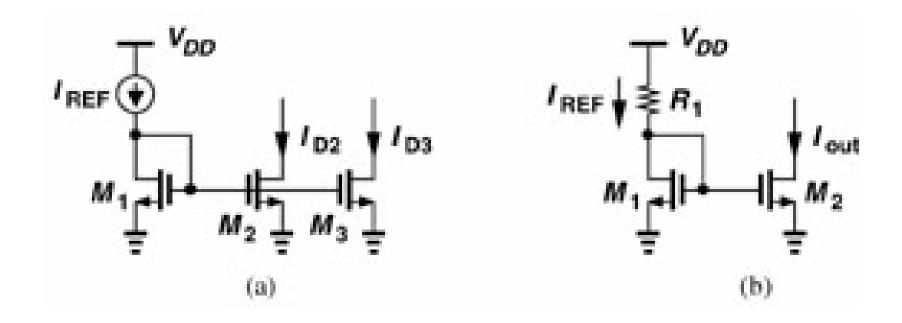

Typically we assume that one precisely defined current source is available and other current sources copy their current from this precise source.

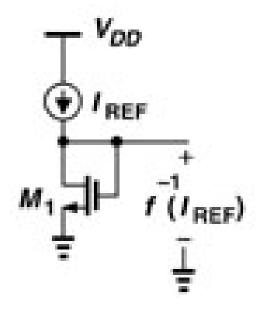

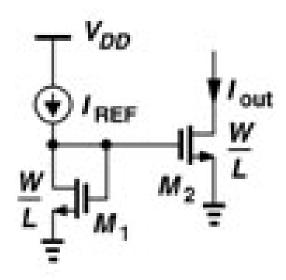

I<sub>out</sub> is a function of gate-source voltage

## Basic Idea

This structure is called current mirror

#### Question

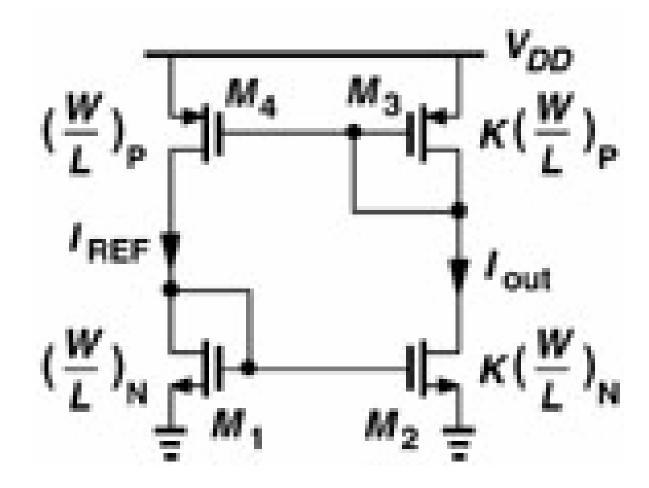

What happens if the two transistors in the basic current mirror have different sizes?

## Example

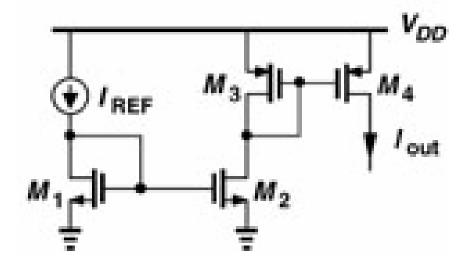

Assuming all the transistors are in saturation region, find I<sub>out</sub>:

# Current Mirrors: Amplifier Bias Example

## **Board Notes**

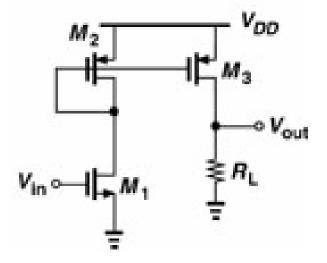

## Current Mirrors: Signal Amplification Example

Find the small signal voltage gain of the following circuit.

## Effect of Channel Length Modulation

## **Board Notes**

## **Board Notes**

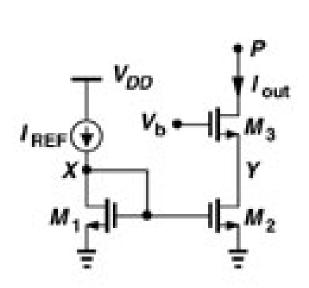

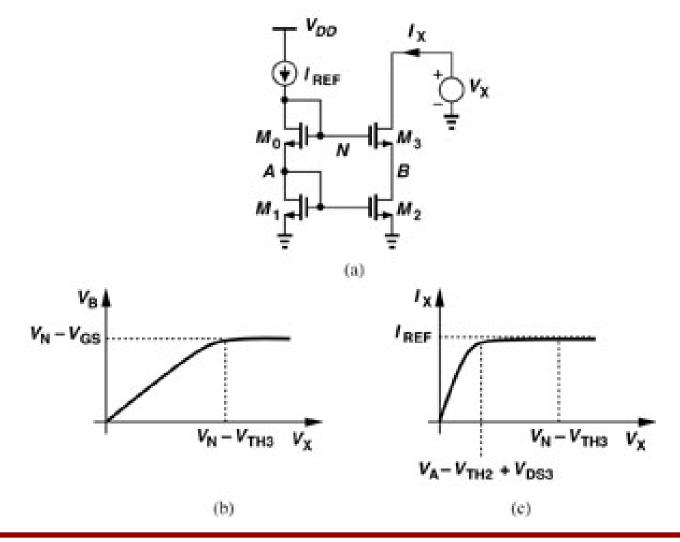

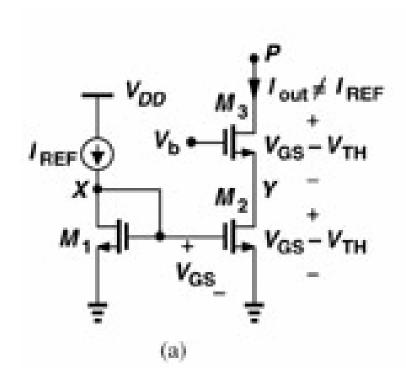

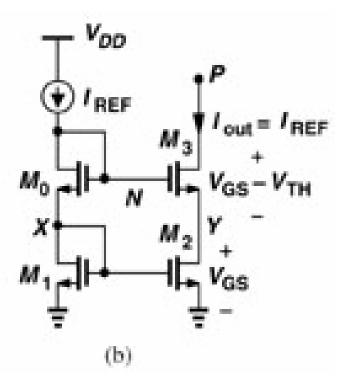

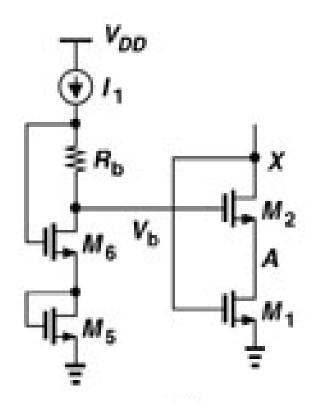

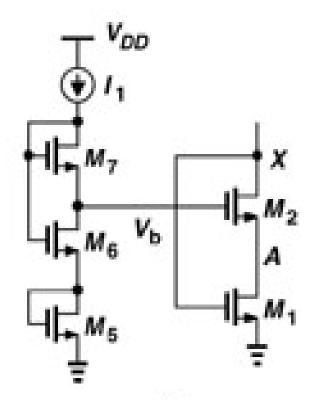

# Cascode Current Mirror Biasing

# Cascode Current Mirror Biasing

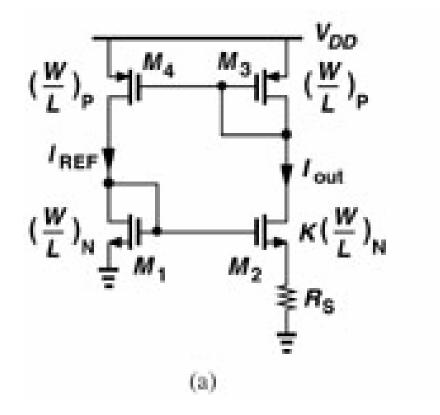

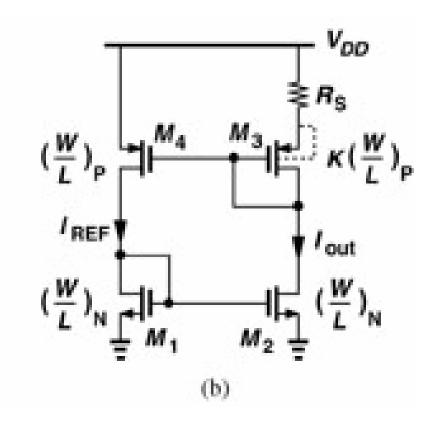

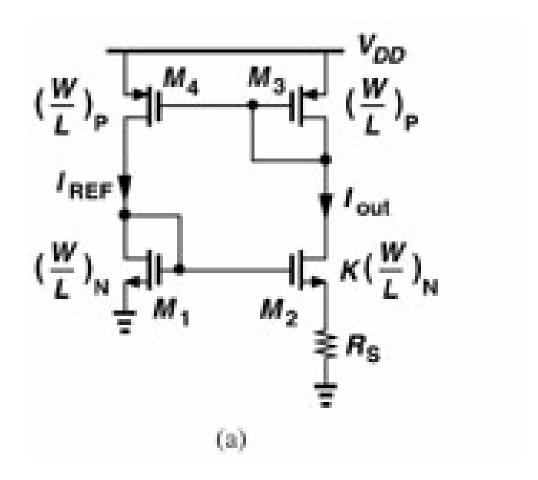

# **Current Mirror Biasing**

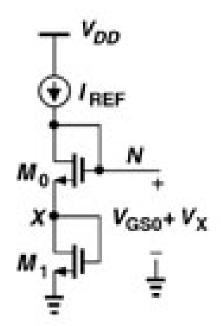

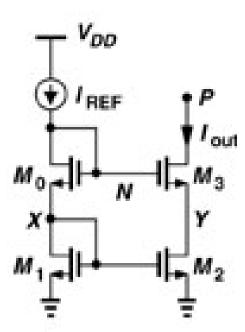

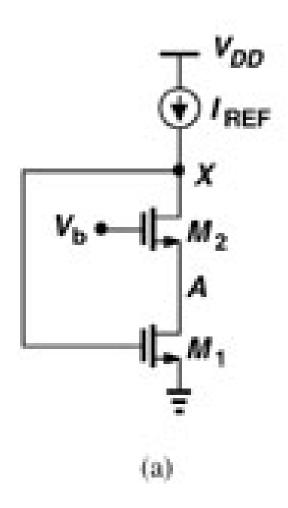

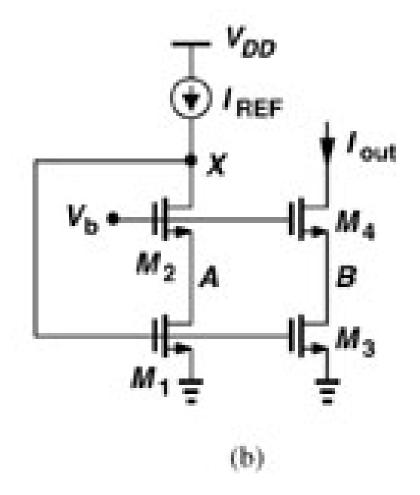

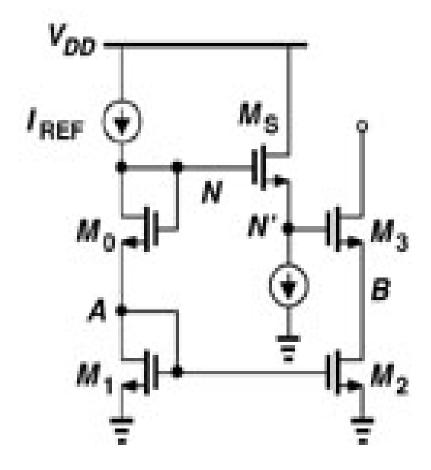

## Basic Circuit to Generate Supply Independent Current

# **Supply Independent Current**

## **Board Notes**

# **Supply Independent Current**

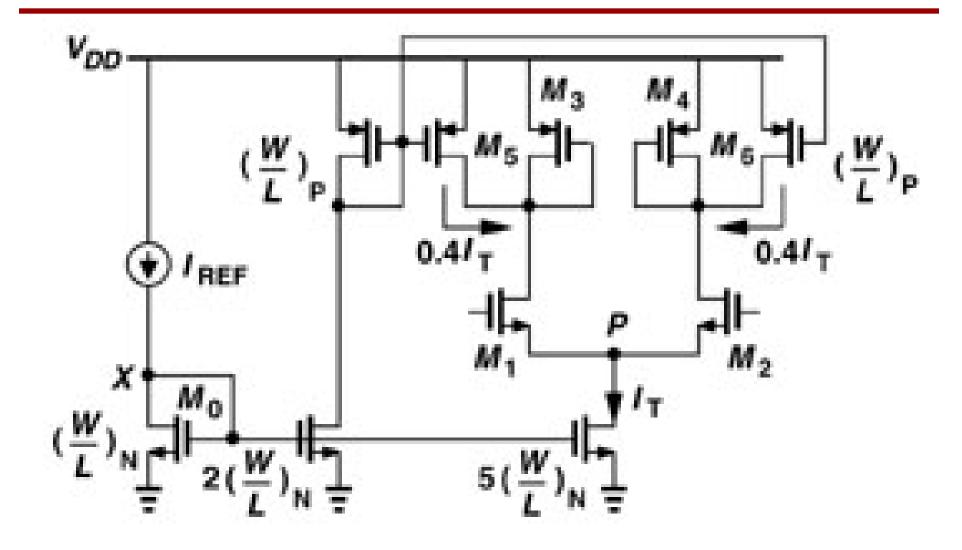

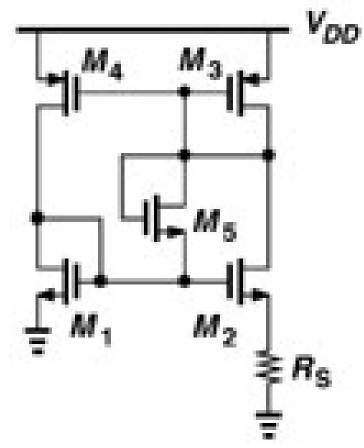

# Start-up Problem

## Start-up Problem

$$V_{TH1} + V_{TH5} + |V_{TH3}| < V_{DD}$$

and  $V_{GS1} + V_{TH5} + |V_{GS3}| > V_{DD}$

## **Board Notes**

#### **Active Current Mirrors**

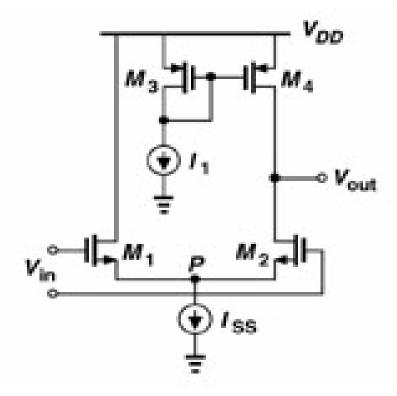

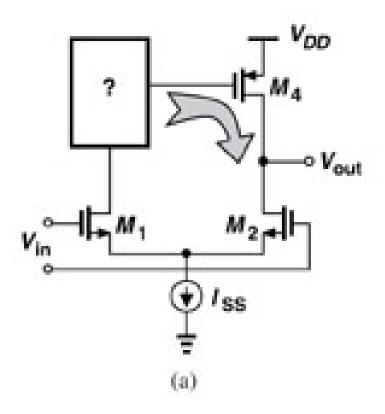

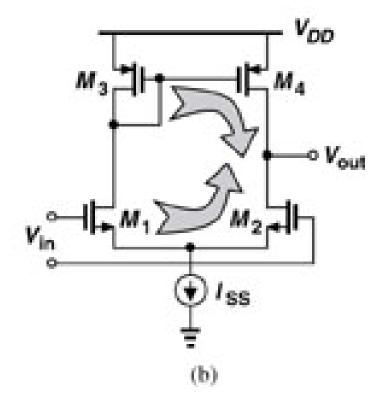

# Active Current Mirrors in Differential to Single-Ended Amplifiers

## Differential to Single-Ended Amplifiers

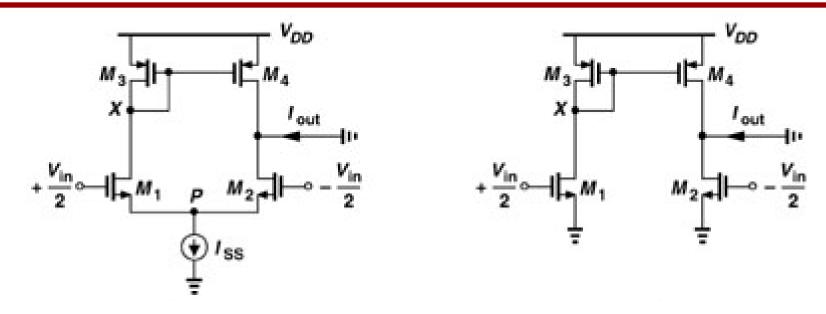

## Calculation of G<sub>m</sub>

$$I_{D1} = I_{D3} = I_{D4} = g_{m1,2}V_{in}/2$$

$I_{D2} = -g_{m1,2}V_{in}/2$

$$I_{out} = I_{D2} - I_{D4} = -g_{m1,2}V_{in} , \Rightarrow G_m = g_{m1,2}$$

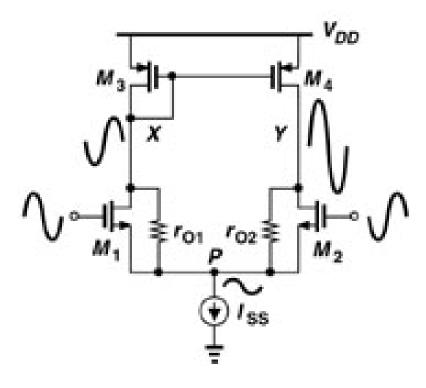

## **Small-Signal Gain**

$$A_{v} \approx g_{m1,2}(r_{o2} || r_{o4})$$

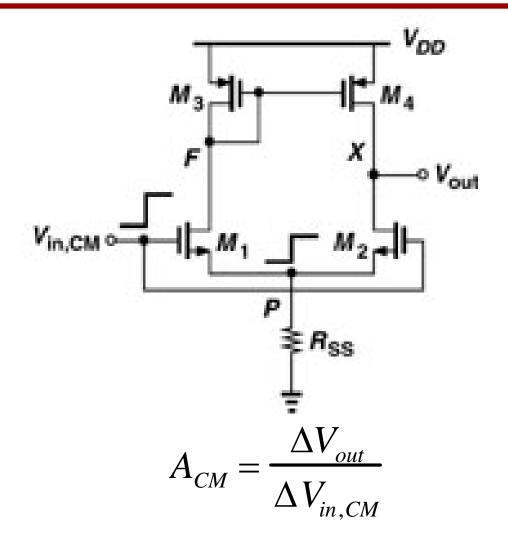

#### **Common Mode Characteristics**

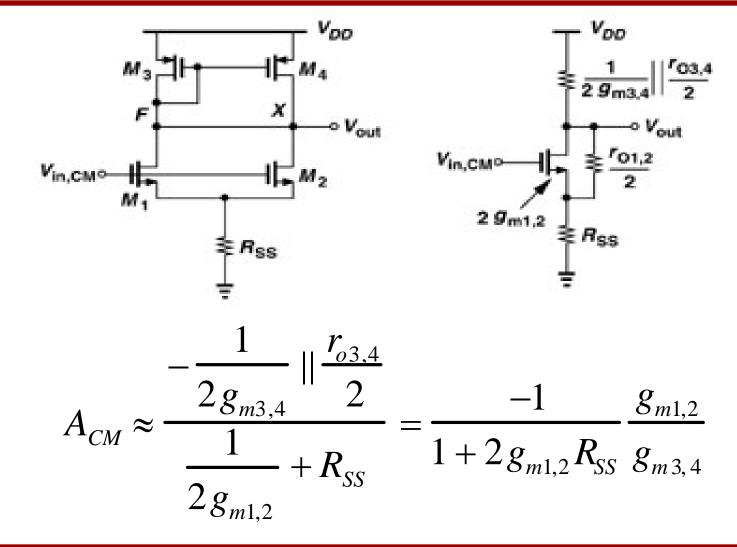

#### Common Mode

#### Common Mode

$$CMRR = \begin{vmatrix} A_{DM} \\ A_{CM} \end{vmatrix}$$

$$= g_{m1,2}(r_{o1,2} || r_{o3,4}) \frac{g_{m3,4}(1 + 2g_{m1,2}R_{SS})}{g_{m1,2}}$$

$$= g_{m3,4}(r_{o1,2} || r_{o3,4})(1 + 2g_{m1,2}R_{SS})$$