## Synchronous Sequential Logic

### Chapter 5

Steve Oldridge Dr. Sidney Fels

|   |             | State |   |            |        |

|---|-------------|-------|---|------------|--------|

|   | sent<br>ate | Input |   | ext<br>ate | Output |

| A | B           | x     | A | В          | y      |

| 0 | 0           | 0     | 0 | 0          | 0      |

| 0 | 0           | 1     | 0 | 1          | 0      |

| 0 | 1           | 0     | 0 | 0          | 1      |

| 0 | 1           | 1     | 1 | 1          | 0      |

| 1 | 0           | 0     | 0 | 0          | 1      |

| 1 | 0           | 1     | 1 | 0          | 0      |

| 1 | 1           | 0     | 0 | 0          | 1      |

| 1 | 1           | 1     | 1 | 0          | 0      |

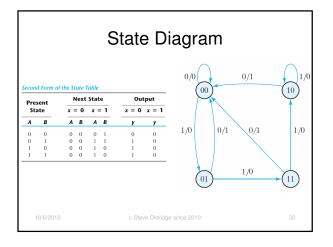

| econ | d Form o | of the St  | ate 1 | Table      |     |       |              |

|------|----------|------------|-------|------------|-----|-------|--------------|

| Pre  | sent     | r          | lext  | Stat       | e   | Out   | put          |

|      | ate      | <i>x</i> = | = 0   | <i>x</i> = | = 1 | x = 0 | <i>x</i> = 1 |

| Α    | В        | A          | B     | A          | B   | y     | Ŷ            |

| 0    | 0        | 0          | 0     | 0          | 1   | 0     | 0            |

| 0    | 1        | 0          | 0     | 1          | 1   | 1     | 0            |

| 1    | 0        | 0          | 0     | 1          | 0   | 1     | 0            |

| 1    | 1        | 0          | 0     | 1          | 0   | 1     | 0            |

|   | sent<br>ate | Input |   | ext<br>ate |    | Flip-F<br>Inpu |                |                |

|---|-------------|-------|---|------------|----|----------------|----------------|----------------|

| A | В           | x     | A | В          | JA | K <sub>A</sub> | J <sub>B</sub> | K <sub>B</sub> |

| 0 | 0           | 0     | 0 | 1          | 0  | 0              | 1              | 0              |

| 0 | 0           | 1     | 0 | 0          | 0  | 0              | 0              | 1              |

| 0 | 1           | 0     | 1 | 1          | 1  | 1              | 1              | 0              |

| 0 | 1           | 1     | 1 | 0          | 1  | 0              | 0              | 1              |

| 1 | 0           | 0     | 1 | 1          | 0  | 0              | 1              | 1              |

| 1 | 0           | 1     | 1 | 0          | 0  | 0              | 0              | 0              |

| 1 | 1           | 0     | 0 | 0          | 1  | 1              | 1              | 1              |

| 1 | 1           | 1     | 1 | 1          | 1  | 0              | 0              | 0              |

| Output |   | Ne:<br>Sta | Input | ent<br>ite | Pres<br>Sta |

|--------|---|------------|-------|------------|-------------|

| y      | B | Α          | x     | В          | A           |

| 0      | 0 | 0          | 0     | 0          | 0           |

| 0      | 1 | 0          | 1     | 0          | 0           |

| 0      | 1 | 0          | 0     | 1          | 0           |

| 0      | 0 | 1          | 1     | 1          | 0           |

| 0      | 0 | 1          | 0     | 0          | 1           |

| 0      | 1 | 1          | 1     | 0          | 1           |

| 1      | 1 | 1          | 0     | 1          | 1           |

| 1      | 0 | 0          | 1     | 1          | 1           |

# How do hardware developers create circuits?

- Visual Layout

- Draw the circuits by connecting components

- Not practical for large scale or VLSI

- Verilog / VHDL

- Describe the circuit's functionality in code

- Run it through a 'compiler'

- Output is a circuit

- Language details are in your text

10/6/201

c Steve Oldridge since 2010

14

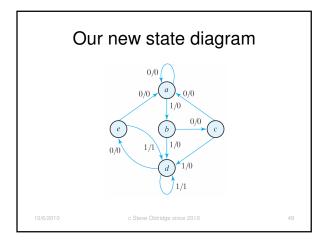

|               | Next  | State        | Out   | put          |

|---------------|-------|--------------|-------|--------------|

| Present State | x = 0 | <i>x</i> = 1 | x = 0 | <i>x</i> = 1 |

| а             | а     | b            | 0     | 0            |

| b             | С     | d            | 0     | 0            |

| С             | а     | d            | 0     | 0            |

| d             | е     | f            | 0     | 1            |

| е             | а     | f            | 0     | 1            |

| f             | g     | f            | 0     | 1            |

| g             | а     | ſ            | 0     | 1            |

|               | Next  | State        | Out   | t <b>put</b> |

|---------------|-------|--------------|-------|--------------|

| Present State | x = 0 | <i>x</i> = 1 | x = 0 | <i>x</i> = 1 |

| а             | а     | b            | 0     | 0            |

| b             | С     | d            | 0     | 0            |

| с             | а     | d            | 0     | 0            |

| d             | е     | f            | 0     | 1            |

| е             | а     | f            | 0     | 1            |

| f             | е     | f            | 0     | 1            |

|              | Next 9 | State        | Outj  | out                     |

|--------------|--------|--------------|-------|-------------------------|

| resent State | x = 0  | <i>x</i> = 1 | x = 0 | <i>x</i> = <sup>-</sup> |

| а            | а      | Ь            | 0     | 0                       |

| b            | С      | d            | 0     | 0                       |

| С            | а      | d            | 0     | 0                       |

| d            | e      | d            | 0     | 1                       |

| е            | а      | d            | 0     | 1                       |

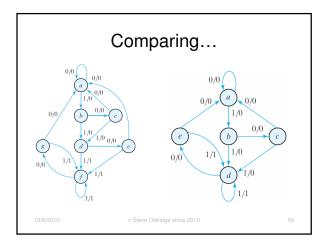

| itate | Assignment 1,<br>Binary | Assignment 2,<br>Gray Code | Assignment 3,<br>One-Hot |

|-------|-------------------------|----------------------------|--------------------------|

| а     | 000                     | 000                        | 00001                    |

| b     | 001                     | 001                        | 00010                    |

| с     | 010                     | 011                        | 00100                    |

| d     | 011                     | 010                        | 01000                    |

| е     | 100                     | 110                        | 10000                    |

| Reduced State Tab | le with Bin | ary Assignn  | nent 1 |              |

|-------------------|-------------|--------------|--------|--------------|

|                   | Next        | State        | Out    | put          |

| Present State     | x = 0       | <i>x</i> = 1 | x = 0  | <i>x</i> = 1 |

| 000               | 000         | 001          | 0      | 0            |

| 001               | 010         | 011          | 0      | 0            |

| 010               | 000         | 011          | 0      | 0            |

| 011               | 100         | 011          | 0      | 1            |

| 100               | 000         | 011          | 0      | 1            |

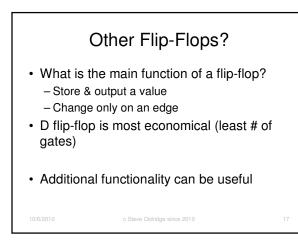

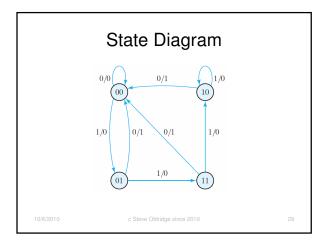

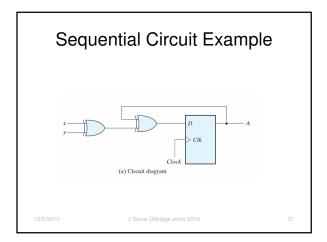

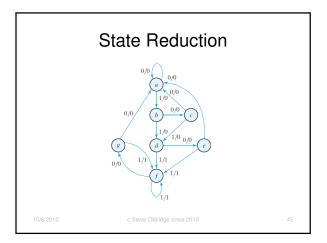

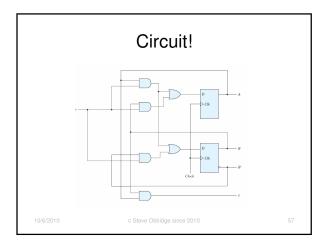

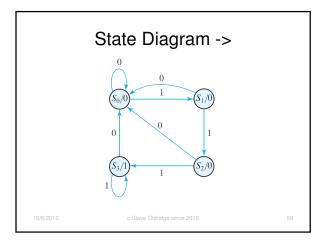

## **Design Procedure**

- Derive a state diagram

- Reduce the number of states

- Assign binary values to states – Integrate this into your state table

- Choose the type of flip-flops

- Derive the flip-flop input and output equations

c Steve Oldridge since 2010

• Draw (or code) the logic diagram

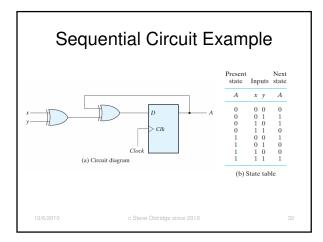

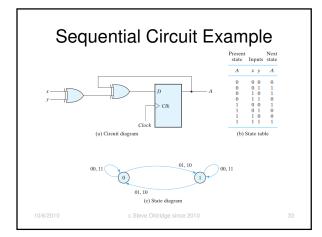

| Pres<br>Sta |   | Input |   | ext<br>ate | Output |

|-------------|---|-------|---|------------|--------|

| A           | В | x     | Α | В          | У      |

| 0           | 0 | 0     | 0 | 0          | 0      |

| 0           | 0 | 1     | 0 | 1          | 0      |

| 0           | 1 | 0     | 0 | 0          | 0      |

| 0           | 1 | 1     | 1 | 0          | 0      |

| 1           | 0 | 0     | 0 | 0          | 0      |

| 1           | 0 | 1     | 1 | 1          | 0      |

| 1           | 1 | 0     | 0 | 0          | 1      |

| 1           | 1 | 1     | 1 | 1          | 1      |

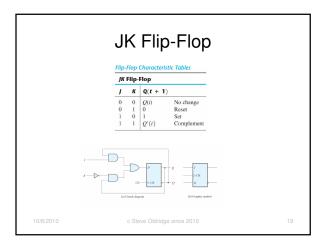

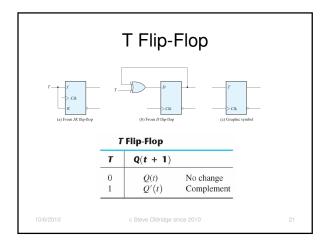

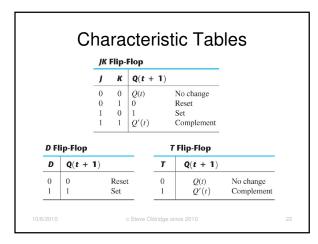

| Q(t) | Q(t = 1)      | J | к | Q(t) | Q(t = 1)     | T |

|------|---------------|---|---|------|--------------|---|

| 0    | 0             | 0 | Х | 0    | 0            | 0 |

| 0    | 1             | 1 | Х | 0    | 1            | 1 |

| 1    | 0             | X | 1 | 1    | 0            | 1 |

| 1    | 1             | Х | 0 | 1    | 1            | 0 |

|      | (a) <i>JK</i> |   |   |      | (b) <i>T</i> |   |

|   | sent<br>ate | Input |   | ext<br>ate | Fli | p-Flop         | Input          | ts |

|---|-------------|-------|---|------------|-----|----------------|----------------|----|

| A | B           | x     | A | В          | JA  | K <sub>A</sub> | J <sub>B</sub> | K  |

| 0 | 0           | 0     | 0 | 0          | 0   | Х              | 0              | Х  |

| 0 | 0           | 1     | 0 | 1          | 0   | Х              | 1              | X  |

| 0 | 1           | 0     | 1 | 0          | 1   | Х              | Х              | 1  |

| 0 | 1           | 1     | 0 | 1          | 0   | Х              | Х              | 0  |

| 1 | 0           | 0     | 1 | 0          | Х   | 0              | 0              | X  |

| 1 | 0           | 1     | 1 | 1          | Х   | 0              | 1              | X  |

| 1 | 1           | 0     | 1 | 1          | Х   | 0              | Х              | 0  |

| 1 | 1           | 1     | 0 | 0          | Х   | 1              | Х              | 1  |

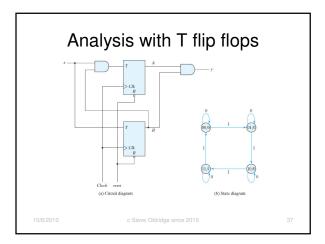

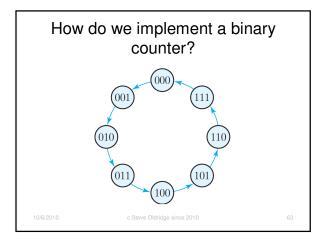

| Present State  |    |                | Next State     |    |                | Flip-Flop Inputs |                 |                        |

|----------------|----|----------------|----------------|----|----------------|------------------|-----------------|------------------------|

| A <sub>2</sub> | A1 | A <sub>0</sub> | A <sub>2</sub> | A1 | A <sub>0</sub> | T <sub>A2</sub>  | T <sub>A1</sub> | <b>T</b> <sub>A0</sub> |

| 0              | 0  | 0              | 0              | 0  | 1              | 0                | 0               | 1                      |

| 0              | 0  | 1              | 0              | 1  | 0              | 0                | 1               | 1                      |

| 0              | 1  | 0              | 0              | 1  | 1              | 0                | 0               | 1                      |

| 0              | 1  | 1              | 1              | 0  | 0              | 1                | 1               | 1                      |

| 1              | 0  | 0              | 1              | 0  | 1              | 0                | 0               | 1                      |

| 1              | 0  | 1              | 1              | 1  | 0              | 0                | 1               | 1                      |

| 1              | 1  | 0              | 1              | 1  | 1              | 0                | 1               | 1                      |

| 1              | 1  | 1              | 0              | 0  | 0              | 1                | 1               | 1                      |

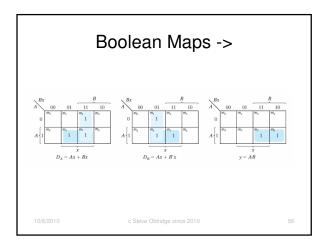

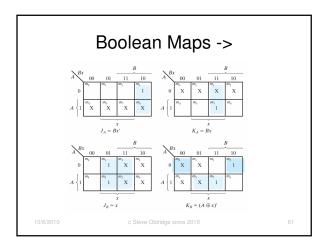

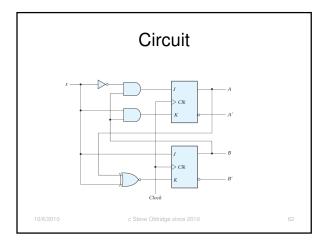

### Sequential Circuit Design Process Review

- Derive a state diagram

- · Reduce the number of states

- Assign binary values to states

Integrate this into your state table

- Choose the type of flip-flops

- Derive the flip-flop excitation table

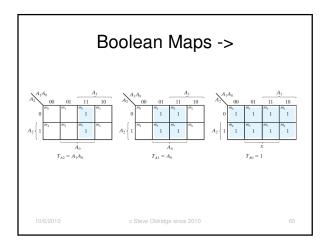

- Create the Boolean Maps

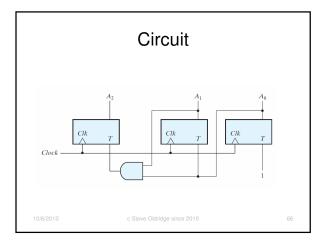

- Draw (or code) the logic diagram

c Steve Oldridge since 2010